# Laminate: Succinct SIMD-Friendly Verifiable FHE

Kabir Peshawaria Zeyu Liu Ben Fisch Eran Tromer Boston University Yale University Yale University Boston University

December 19, 2025

#### Abstract

In outsourcing computation to untrusted servers, one can cryptographically ensure privacy using Fully Homomorphic Encryption (FHE) or ensure integrity using Verifiable Computation (VC) such as SNARK proofs. While each is practical for some applications in isolation, efficiently composing FHE and VC into *Verifiable Computing on Encrypted Data (VCoED)* remains an open problem.

We introduce Laminate, the first practical method for adding integrity to BGV-style FHE, thereby achieving VCoED. Our approach combines the blind interactive proof framework with a tailored variant of the GKR proof system that avoids committing to intermediate computation states. We further introduce variants employing transcript packing and folding techniques. The resulting encrypted proofs are concretely succinct: 270 kB, compared to 1 TB in prior work, to evaluate a batch of  $B=2^{14}$  instances of size  $n=2^{20}$  and depth d=32. Asymptotically, the proof size and verifier work is  $O(d\log(Bn))$ , compared to  $\Omega(BN\log n)$  in prior work (for ring dimension N).

Unlike prior schemes, Laminate utilizes the full SIMD capabilities of FHE for both the payload circuit evaluation and proof generation; adds only constant multiplicative depth on top of payload evaluation while performing  $\tilde{O}(n)$  FHE operations; eliminates the need for witness reduction; and is field-agnostic. The resulting cost of adding integrity to FHE, compared to assuming honest evaluation, is  $\sim 12 \times$  to  $\sim 36 \times$  overhead (for deep multiplication-heavy circuits of size  $2^{20}$ ), which is  $> 500 \times$  faster than the state-of-the-art.

# Contents

| 1 | Intr | roduction                                                   | 4  |

|---|------|-------------------------------------------------------------|----|

|   | 1.1  | Challenges in FHE-over-SNARK VCoED                          | 4  |

|   |      | 1.1.1 Challenges for Server Efficiency                      | 5  |

|   |      | 1.1.2 Challenges for Client Efficiency                      | 6  |

|   | 1.2  | Our Contribution                                            | 7  |

|   | 1.3  | Related Work                                                | 8  |

|   | 1.4  | Technical Overview                                          | 9  |

|   | 1.5  | Summary of Evaluation                                       | 12 |

|   |      | 1.5.1 Comparisons with Prior Works                          | 12 |

|   |      | 1.5.2 Comparisons with Honest Payload Generation            | 13 |

| 2 | Pre  | eliminaries                                                 | 13 |

|   | 2.1  | (Leveled) Homomorphic Encryption                            | 13 |

|   | 2.2  |                                                             | 14 |

|   | 2.3  |                                                             | 14 |

|   | 2.4  |                                                             | 15 |

|   | 2.5  | The Blind SNARG Compilation                                 | 15 |

|   | 2.6  | Multilinear Polynomials and Multilinear Extensions          | 16 |

|   | 2.7  | Multivariate Sumcheck Protocol                              | 17 |

| 3 | Rec  | quisite hIOP and HE Schemes                                 | 18 |

|   | 3.1  | GKR Protocol                                                | 18 |

|   |      | 3.1.1 The Layer Reduction Subroutine                        | 19 |

|   |      | 3.1.2 Round Complexity and Proof Size                       | 20 |

|   |      | 3.1.3 Leveraging Circuit Structure                          | 22 |

|   |      | 3.1.4 Algorithmically Dealing with Gate Indicator Functions | 22 |

|   |      | 3.1.5 Other Remarks                                         | 23 |

|   | 3.2  | BGV/BFV FHE Protocol                                        | 23 |

| 4 | GK   | R-inspired Blind Holographic IOPs                           | 25 |

|   | 4.1  | Overview and Prerequisites                                  | 25 |

|   |      | 4.1.1 Class of Supported Payload Circuits                   | 26 |

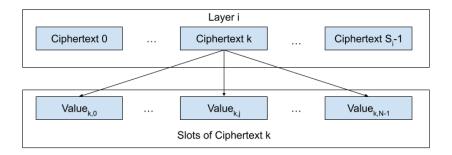

|   |      | 4.1.2 Data Layout and Notation                              | 26 |

|   |      | 4.1.3 The folding operator                                  | 27 |

|   | 4.2  | Warmup: BhIOPs for Rotation-Free Payload Circuits           | 28 |

|   |      | 4.2.1 Description of Rotation-Free GKR hIOPs                | 28 |

|   |      | 4.2.2 Operation Counts                                      | 29 |

|   | 4.3  | General Case: BhIOPs for Layered Payload Circuits           | 29 |

|   |      | 4.3.1 $(c, f)$ -layered GKR hIOP Description                | 31 |

|   |      | 4.3.2 Operation Counts                                      | 32 |

|   | 4.4  | Summary: Base vs Folded BhIOP variants                      | 33 |

|   | 4.5  | Active Slots and Batching                                   | 34 |

| 5            | Ach | ieving Efficient VCoED                                                        | 35         |

|--------------|-----|-------------------------------------------------------------------------------|------------|

|              | 5.1 | Sub-optimality of Previous Blind SNARG Compilation                            | 35         |

|              | 5.2 | Transcript Packing: New BIOP to BIP Compiler                                  | 35         |

|              |     | 5.2.1 Compiler Description                                                    | 36         |

|              |     | 5.2.2 Proof of Theorem 5.1                                                    | 36         |

|              |     | 5.2.3 Cost Analysis of Computing Outer SNARK $\pi_{\text{outer}}$             | 38         |

|              | 5.3 | End to End VCoED from Blind Holographic SNARGs                                | 40         |

|              | 5.4 | Family of VCoED Protocols                                                     | 40         |

|              |     | 5.4.1 Efficiency Parameters and Notation                                      | 40         |

|              |     | 5.4.2 Laminate <sub>base</sub> : Base BhIOP with Trivial Compiler             | 42         |

|              |     | 5.4.3 Laminate <sub>fold</sub> : Folded BhIOP with Transcript Packing         | 42         |

|              |     | 5.4.4 Laminate <sub>pack</sub> : Base BhIOP with Transcript Packing           | 43         |

| 6            | Eva | luation                                                                       | 44         |

|              | 6.1 | Implementation Considerations                                                 | 44         |

|              | 6.2 | Methodology                                                                   | 45         |

|              | 6.3 | Comparisons                                                                   | 46         |

|              | 6.4 | Overhead Compared to Honest Evaluation                                        | 48         |

| A            | Pro | of of Lemma 3.7                                                               | <b>56</b>  |

| В            | Gru | nen Section 3 Optimization                                                    | 57         |

| $\mathbf{C}$ | BhI | OP Operation Counts                                                           | <b>5</b> 9 |

|              | C.1 | Base BhIOP Prover FHE Operations for Rotation-Free Payload Circuits           | 59         |

|              |     | C.1.1 Overview and Notation                                                   | 59         |

|              |     | C.1.2 Computing the Layer Reduction Sumcheck Round Polynomial under FHE       | 60         |

|              |     | C.1.3 Total cost of GKR prover under FHE                                      | 65         |

|              | C.2 | Folded BhIOP Prover FHE Operations for Rotation-Free Payload Circuits         | 66         |

|              |     | C.2.1 Compute-Only Layer Reduction Operation Counts for Folded BhIOP Prover . | 66         |

|              |     | C.2.2 Total Operation Counts                                                  | 67         |

|              | C.3 | Base BhIOP Prover FHE Operations for $(c,f)$ -Layered Payload Circuits        | 68         |

|              |     | C.3.1 Operation Counts for Compute-Only Layer Reductions                      | 68         |

|              |     | C.3.2 Operation Counts for Forward-Only Layer Reduction                       | 68         |

|              | C.4 | Folded BhIOP Prover FHE Operations for $(c, f)$ -Layered Payload Circuits     | 68         |

|              | 0.1 |                                                                               |            |

|              | 0.1 | C.4.1 Operation Counts for Compute-Only Layer Reductions                      | 69<br>69   |

### 1 Introduction

Delegation of expensive computation to cloud services is common nowadays, and raises privacy issues when clients' data is private or sensitive. Fully homomorphic encryption (FHE) [41] is a powerful cryptographic tool for *private* delegation of computation: it enables a server to perform arbitrary computations directly on encrypted data, without learning the underlying plaintext. Over the past decade, a series of breakthroughs [16, 31, 25, 23, 15, 14, 32] improved the efficiency of FHE, making it increasingly practical for some classes of privacy-sensitive delegation applications, including machine learning [51, 47, 52, 48, 29], secure data processing [40], private information retrieval [3, 65, 35, 82, 46], private set intersection [21, 20, 26], oblivious message retrieval [58, 59, 60, 53, 57], and single secret leader election [12, 77].

Despite its power, FHE inherently lacks integrity guarantees for computation: it is sound only if the server is honest. A malicious server can arbitrarily alter the computation results by evaluating a circuit of their choice instead of the intended one. Even though the server cannot directly observe the decrypted output, it can for example choose that output to be a maliciously-chosen value that harms the client, or some function of the secret inputs that would cause observable client behavior from which the secret can be deduced. To address this, Gennaro, Gentry, and Parno [40] introduced the concept of Verifiable Computation over Encrypted Data (VCoED). VCoED enables computation delegation to an untrusted server while (1) preserving data confidentiality and (2) allowing the client to verify the correctness of the computation. However, achieving efficient VCoED remains an open problem for over a decade.

One approach to realizing VCoED is using cryptographic proofs of FHE evaluation. Specifically, SNARKs (Succinct Non-interactive Arguments of Knowledge), allow the server to produce a succinct proof that its output is indeed the result of applying all the designated ciphertext evaluations correctly. While powerful, this approach suffers from very high proving costs, as known SNARKs inefficiently handle statements about *non-algebraic* ciphertext operations (e.g. relinearization).

A recent line of work [38, 4, 36, 81] explores an alternative approach to VCoED: FHE-over-SNARK, which flips the order of composition: it uses FHE to homomorphically compute the SNARK proof in encrypted form. The server first homomorphically evaluates the payload circuit storing ciphertexts representing intermediate wires. It then homomorphically evaluates the circuit of a SNARK prover on the statement corresponding to the desired circuit, and with inputs represented by the above ciphertexts. All these values, as well as the resulting SNARK proof, remain encrypted and hidden from the server. A malicious server could still manipulate the payload circuit evaluation and send an incorrect output, but this will be detected when the client decrypts and verifies the received proof.

The FHE-over-SNARK approach appears to yield much better performance than providing SNARK proofs of the whole homomorphic evaluation — intuitively, because one pays the combined overhead of FHE and SNARK not for computing the payload circuit, but rather, only when homomorphically evaluating the SNARK prover applied to the wires of that circuit. Unlike the payload circuit, the SNARK can be chosen to be very structured and particularly amenable to FHE evaluation. However, substantial challenges remain, as explained next.

### 1.1 Challenges in FHE-over-SNARK VCoED

While the FHE-over-SNARK paradigm is promising, current realizations [4, 36, 81] remain impractical. They impose expensive overheads on the server and require a high bandwidth client capable of processing large proofs.

<sup>&</sup>lt;sup>1</sup>SNARG (Succinct Non-Interactive Argument) suffices, as knowledge-soundness is not needed here.

### 1.1.1 Challenges for Server Efficiency

Inherent challenges stem from the setting of BFV/BGV homomorphic evaluation: multiplicative depth is very costly, the native algebraic structure is constrained, and performance relies on utilizing a very restrictive form of parallelism. Key examples follow.

Witness reduction overheads. An often-overlooked cost in SNARK-based verifiable computation is the witness reduction. After evaluating the desired payload computation and storing all the intermediate values, there can be an additional cost to transform these to the representation that the SNARK prover can handle (sometimes referred to as the *extended witness*).

A prominent case of such overhead occurs due to mismatched fields and non-native arithmetic. For instance, a payload computation consisting of a single  $\mathbb{F}_q$  addition would intuitively require a proof for a single addition. However, if the SNARK prover operates over a different field  $\mathbb{F}_p$  (with  $p \neq q$ ), this is not the case:  $x_1 + x_2 \equiv x_3 \pmod{p}$  does not imply that  $x_1 + x_2 \equiv x_3 \pmod{q}$ . Hence, the  $\mathbb{F}_p$ -based constraint system must emulate  $\mathbb{F}_q$  arithmetic, which increases the constraint count and requires many additional witness variables to be homomorphically computed.

This problem is particularly severe in the FHE setting, where non-native arithmetic often requires operations like modular inverse, which are prohibitively expensive in terms of multiplicative depth. For example, computing  $x^{-1} \pmod{q}$  via  $x^{q-2} \pmod{q}$ , via Fermat's Little Theorem, requires  $\Theta(\log q)$  iterated modular multiplications, adding significant multiplicative depth to the homomorphic evaluation before even starting the prover evaluation.

Prior FHE-over-SNARK schemes largely overlook this challenge. For instance, [81] fixes the SNARK's base field at 50 bits. This is a poor match for many BFV/BGV applications [15, 14, 32], which use much smaller plaintext fields (e.g., < 20 bits in [58, 60, 35]) for efficiency. Forcing a 50-bit field can slow down the underlying FHE computation by over  $20 \times .^2$  Similarly, [36] employs generalized BFV/BGV (GBFV/GBGV) instead of standard variants, but this workaround comes at a high cost: GBFV provides  $16 \times$  fewer plaintext slots than BFV, reducing evaluation throughput by the same factor.

Inefficient proof generation due to polynomial commitments. Prior works' server efficiency is bottlenecked by reliance on polynomial commitments (PCs) for the extended witness, which contains all intermediate values that arose during payload computation. Concretely, [36, 81] use hashing-based PCs, which are typically computed using the Number Theoretic Transform (NTT). Though an NTT over a length-n vector can be done in  $O(n \log n)$  time, this can only be achieved at the cost of  $\Omega(\log n)$  multiplicative depth. To achieve multiplicative depth  $\leq t$ , NTT requires  $\Omega(t \cdot n^{1+1/t})$  operations.

For an n-gate payload circuit, the Fractal [24] proof system used in [36] requires an NTT over a length n vector. For [81], the situation is more complicated (see Section 1.1.2), but the NTTs that arise are still large enough to preclude a prover circuit that runs in  $\tilde{O}(n)$  with constant multiplicative depth. High multiplicative depth in the prover circuit inflates the noise budget required for the entire FHE evaluation, including the original payload circuit. That is, a payload circuit of depth d would now require the FHE scheme to support a total depth of  $d + \omega(1)$  by reserving sufficient noise or bootstrapping  $\omega(1)$  times. FHE performance is highly sensitive to this total depth parameter.

Loss of FHE Parallelism. Prior schemes [36, 81] use BFV/BGV encryption, which offers parallelism via SIMD (Single Instruction, Multiple Data) computation that concurrently operates on

<sup>&</sup>lt;sup>2</sup>For example, in [58, 60], the multiplicative depth is  $\sim \log p$  for a plaintext space  $\mathbb{Z}_p$ . Consequently, increasing the plaintext modulus from a  $\sim$ 20-bit field to a 50-bit field raises the required depth from  $\sim$ 20 to  $\sim$ 50. Moreover, a larger plaintext space incurs higher noise growth per level, increasing the total noise budget from approximately  $\sim$ (20 × 30) to  $\sim$ (50 × 60). This alone results in a runtime overhead of at least  $\sim$ 5×. In addition, maintaining the same security level requires increasing the ring dimension by  $\geq$  4×, implying that the overall runtime overhead exceeds 20×.

N "slots", typically with  $N \approx 2^{14}$  or larger. However, all this capacity for parallel computation and storage is allocated to the prover circuit, and specifically to accelerating the expensive polynomial commitment schemes. The actual payload computation is performed in a single slot, without parallelism. Conversely, virtually all practical applications using BFV/BGV FHE (e.g., [58, 35, 21, 20, 26]) rely on SIMD parallelism being fully available and utilized by the payload computation. Reducing these to "single-threaded" execution (by using a single slot for the payload circuit) immediately reduces the system throughput by a factor of tens of thousands, making the total cost of adding integrity exorbitantly expensive even accounting for the additional costs of witness reduction and evaluation of the prover circuit.

#### 1.1.2 Challenges for Client Efficiency

Ideally, VCoED scheme minimizes communication and client verification time. In an attempt to improve server efficiency, current FHE-over-SNARK schemes sacrifice this desideratum.

FHE-friendly polynomial commitments imply larger proofs. Previous attempts to realize VCoED through FHE-over-SNARK were built from proof systems based on the Polynomial IOP (PIOP) framework [17]. These proof systems require committing to a polynomial whose total degree is linear in the size of the extended witness. As discussed above, the requisite polynomial commitments do not admit both a constant multiplicative depth and quasi-linear time prover. To accelerate these commitments, prior works heavily exploit SIMD techniques, i.e. the fact that one BGV/BFV operation performs N operations on the underlying plaintext space (where N is the BGV/BFV ring dimension).

Blind Fractal server [36] has  $\Omega(N \log n)$  size proofs and performs  $\Omega(tn^{1+\frac{1}{t}}N^{-1})$  operations to compute an NTT on an extended witness vector of length n in multiplicative depth t. Notably, this server only runs in quasi-linear time in a parameter regime where  $N = \tilde{\Omega}(n^{1/t})$ . Thus, to homomorphically evaluate a Fractal prover circuit in  $\tilde{O}(n)$  FHE operations and multiplicative depth < t, proof size and verifier time is at least  $\tilde{\Omega}(n^{1/t})$ .

Phalanx [81] improves the server efficiency, but with worse asymptotic implications to its client. It uses the Ligero/Brakedown PCS [2, 43],<sup>3</sup> which rather than performing one NTT of a length n vector, performs  $\sqrt{n}$  NTTs over length  $\sqrt{n}$  vectors.<sup>4</sup> The consequence is that the [81] server can homomorphically evaluate its polynomial commitment in multiplicative depth t with  $\Omega(tn^{1+\frac{1}{2t}}N^{-1})$  FHE operations. However, these commitments require opening proofs of size  $\Omega(n^{0.5})$ . The proof size and client verification time of [81] are at least  $\Omega(N \log n + \sqrt{n})$ .

Concretely impractical proof sizes and verification time. Prior works such as [36, 81] discuss parameter regimes that make homomorphically evaluating the SNARK proof more tractable. However, the highlighted parameters are too server-friendly, coming at great cost to the client.

Concretely, [36, 81] benchmark their schemes for payload circuits with  $n=2^{20}$  gates using  $N=2^{14}$  SIMD slots. For this choice, [81] yields proofs of 58 MB, while [36] proof sizes are 116 MB (for a single instance). However, simply writing down all  $2^{20}$  wire assignments requires only 17 MB (for a plaintext modulus  $q \leq 2^{128}$ ). The client would be more memory-efficient, and faster, if it just performed the payload computation locally without delegation.

<sup>&</sup>lt;sup>3</sup>Specifically, the Phalanx server [81] homomorphically evaluates the proof system defined by the Spartan [70] PIOP, compiled with a PCS that is implicit in Ligero [2] and explicitly given in Brakedown [43].

<sup>&</sup>lt;sup>4</sup>More generally, the Brakedown [43] PCS constructs an  $m \times n/m$  matrix and performs an NTT on each n/m sized row. An opening proof consists of m field elements. Phalanx [81] does not explicitly state the chosen matrix dimensions, but the setting  $m = \sqrt{n}$  is implied by Section 5.1 stating that the depth-t commitment requires  $O(tn^{1+\frac{1}{2t}}) = O(n^{0.5} \cdot tn^{0.5(1+1/t)})$  operations. Also, this PCS can be generalized beyond a matrix, to a tensor of dimension up to  $\log n$  [13]; this was not explored by [81].

Thus, in this work, we ask the following question:

Can we build an FHE-over-SNARK construction that:

- (1) has a quasi-linear prover circuit with constant multiplicative depth;

- (2) achieves succinct proof size and verification time (polylogarithmic in payload circuit size);

- (3) natively supports SIMD amortization; and (4) is field-agnostic?

We answer affirmatively by showing such a construction and showing its concrete efficiency.

#### 1.2 Our Contribution

We introduce Laminate, a family of three protocols for Verifiable Computation over Encrypted Data that follow the FHE-over-SNARK paradigm. Laminate protocols perform fully-parallel BFV/BGV homomorphic evaluation of payload circuits, combined with homomorphic evaluation of (a variant of) Goldwasser-Kalai-Rothblum [42] proofs to ensure correctness.<sup>5</sup>

Laminate is the first concrete VCoED scheme to achieve the following properties:

Quasi-linear server circuit with constant multiplicative depth overhead. The multiplicative depth overhead for adding integrity is asymptotically *constant*, and concretely 1.5, 2.5, or 3.5 levels depending on the variant of Laminate (i.e., with a tradeoff against proof size). The resulting noise budget overhead is only 50-120 bits (for < 20-bit plaintext field).

Furthermore, the servers performs  $O(n \log n)$  FHE operations in all parameter regimes. This is possible because Laminate avoids committing to the extended witness.

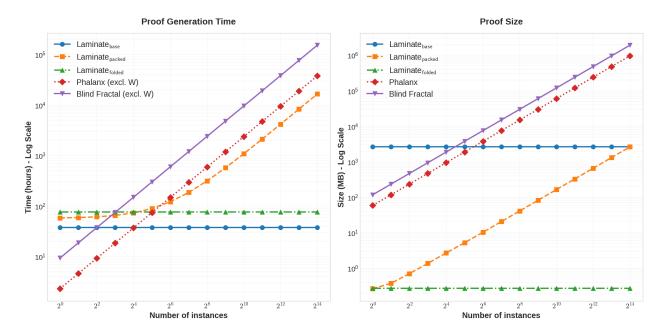

Native SIMD Amortization. Laminate preserves the native SIMD capabilities of BFV/BGV, allowing the payload circuit to utilize all N available slots, unlike prior works. To quantify this advantage, comparing<sup>7</sup> against Phalanx [81] with a payload circuit of  $n = 2^{20}$  gates and ring dimension  $N = 2^{14}$ :

- For a batch of 32 instances, all variants of Laminate achieve faster server runtimes.

- At full capacity (a batch of N instances), the Laminate<sub>fold</sub> server is  $500 \times$  faster and the Laminate<sub>base</sub> server is  $1000 \times$  faster.

Succinct Proof Sizes and Verifier Efficiency. Laminate<sub>fold</sub>, our variant optimized for the client, is succinct, e.g. both proof size and verifier runtime are  $O(N+d\log(Nn))$ . Moreover, this is achieved while keeping the server circuit constant multiplicative depth and quasi-linear (in FHE operations). The novel technical ingredient is a "transcript packing" technique that is described in Theorem 5.1. No prior work achieved all of the above properties; see a comparison in Table 1.8

For the concrete common parameter set considered by prior work (i.e.  $n = 2^{20}$  gates,  $N = 2^{14}$  slots) where we batch N disjoint instances, Laminate fold produces proofs that are  $3,500,000 \times$  smaller

<sup>&</sup>lt;sup>5</sup>The name Laminate alludes to the proof generation comprising a thin layer of extra computation, with very low multiplicative depth, that is added on top of the bulk of payload computation to ensure its integrity.

<sup>&</sup>lt;sup>6</sup>We count scalar-by-ciphertext as 0.5 multiplicative levels, because they consume less noise than plaintext-by-ciphertext or ciphertext-by-ciphertext multiplication. We also assume that extension field multiplication can be done by a depth-1 circuit; otherwise add at most 0.5 levels, per Remark 6.1.

<sup>&</sup>lt;sup>7</sup>The full end-to-end server runtime advantage is greater than the above bounds, since prior work did not account for a few critical costs; see Section 1.5.

<sup>&</sup>lt;sup>8</sup>Laminate requires the payload circuit to be *layered*, i.e. gates in layer i take inputs from layer i+1. Circuits that arise from natural computations are typically layered, or can undergo an inexpensive transformation to become layered (by adding forwarding dummy gates), as discussed in Section 3.1.5. For payload circuits intended to be evaluated under FHE without bootstrapping, Laminate variants support a gate set for which the payload circuit can be viewed as having d = O(1) layers (see Remark 4.6).

<sup>&</sup>lt;sup>9</sup>For ease of comparison to prior works, we benchmark the setting of using a single SIMD slot per instance, though unlike those works, Laminate can also handle more general payload circuits that use multiple slots for a single instance (including cross-slot rotation gates).

| Protocol                 | Mult Depth Overhead | Server FHE Ops                                        | Proof Size                     | Use Case                        |

|--------------------------|---------------------|-------------------------------------------------------|--------------------------------|---------------------------------|

| Laminate <sub>base</sub> | 1.5 Levels          | $O(n \log n)$                                         | $O(Nd\log n)$                  | High Throughput $(k \approx N)$ |

| Laminatepack             | 2.5 Levels          | $O(n \log n)$                                         | $O(\max\{kd\log n, N\})$       | Sparse Computation $(k \ll N)$  |

| Laminate <sub>fold</sub> | 3.5 Levels          | $O(n\log(kn) + d\log(kn)\log k)$                      | $O(\max\{d\log(kn), N\})$      | Bandwidth Constrained           |

| Phalanx [81]             | t+3 Levels          | $\Omega(\frac{k}{N}(n\log n + tn^{\frac{2t+1}{2t}}))$ | $\Omega(k\sqrt{n} + kN\log n)$ | 2PC (private server inputs)     |

| Blind Fractal [36]       | 3t + 3 Levels       | $\Omega(\frac{k}{N}(n\log n + tn^{\frac{t+1}{t}}))$   | $\Omega(kN\log n)$             | ZKP Delegation                  |

Table 1: Comparison of VCoED Protocols for single-slot payload circuits with n gates and d layers, batched with  $k \in [1, N]$  disjoint instances (where N denotes the BGV/BFV SIMD slot capacity). Lower bounds are used for prior work since some end-to-end costs were omitted in their evaluation, as discussed in Section 1.5. The parameter t (for prior work) denotes a tunable multiplicative depth for evaluating an NTT (or inverse NTT) under FHE. For all protocols, the client's runtime is linear in the proof size.

than Phalanx [81], and Laminate<sub>base</sub> (optimized for server efficiency) produces proofs  $365 \times$  smaller. Field-agnostic. Laminate protocols are agnostic of the plaintext field, thereby avoiding additional costs that come with forcing the delegated computation to be defined over a fixed large field and emulating non-native arithmetic.

Conceptual simplicity. The protocol separates logically into two phases: the payload evaluation and the proof evaluation. Crucially, the proof generation accepts the intermediate ciphertexts of the payload evaluation as is. This removes the need for witness reduction or extended witness formatting. In its simplest form (Laminate<sub>base</sub>), the protocol relies solely on a leveled homomorphic evaluation of the multivariate sum-check protocol, avoiding the complexity of Polynomial Interactive Oracle Proofs (PIOPs).

### 1.3 Related Work

FHE-over-SNARK. The paradigm of homomorphically generating a proof under FHE for Verifiable Computation on Encrypted Data (VCoED) was first proposed by [38]. A sequence of follow-up works [4, 36, 81] attempt to realize this new paradigm with concrete efficiency. HELIOPOLIS [4] instantiates it using a homomorphic evaluation of the FRI Interactive Oracle Proofs (IOP). Blind Fractal [36] utilizes the Fractal proof system, while Phalanx [81] employs the Spartan polynomial interactive oracle proof (PIOP) system. Notably, these works extend the utility of FHE-over-SNARK to broader cryptographic objectives beyond basic VCoED:

- ZK Proof Delegation: Blind Fractal [36] applies this paradigm to delegate the generation of a zero-knowledge proof. A client provides the instance and an encrypted witness to a server, which homomorphically evaluates the ZK-SNARK prover circuit. While the resulting proof is initially a designated-verifier proof, the client can subsequently generate a recursive proof to demonstrate knowledge of the secret key required for verification.

- Maliciously Secure 2PC: Phalanx [81] leverages FHE-over-SNARK to achieve maliciously secure Two-Party Computation (2PC). Here, FHE ensures the privacy of the client's inputs, while the server homomorphically evaluates a ZK-SNARK and re-randomizes the resulting ciphertexts. The ZK property ensures the server's private inputs remain hidden from the client, while the soundness of the SNARK guarantees the client receives the correct result.

However, all of these works suffer from the issues discussed in Section 1.1. We compare the concrete efficiencies in more detail in Section 6.

**SNARK-over-FHE.** Many works have tried to use SNARKs to directly prove that homomorphic operations are done correctly. There is a rich history here of co-designing a SNARK and FHE

combination such that the SNARK can efficiently prove supported ciphertext operations, and supporting operations so that the FHE computation (sans proof) itself is not made much less efficient. The first notable work to try this approach was in [34], which built a SNARK whose constraints are native to a quotient polynomial ring, like those used in Ring-LWE based HE constructions, rather than a finite field. A followup work [11] modifies the SNARK to operate over an unquotiented polynomial ring, citing gains in prover efficiency. However, constraints of either ring still struggle to capture verifying ciphertext operations such as relinearization were performed correctly. Likewise, [37] struggles to verify these same ciphertext operations, and thus cannot support arbitrary depth computations. Later, [5] solved this limitation, designing a SNARK scheme that can prove FHE (as opposed to SHE) computations. However, these approaches still remain of theoretical interest as costs are impractical for circuits that require multiple levels of multiplicative depth. For further discussion, see the analysis in [76].

Other work [75, 56] proves that an FHE bootstrapping procedure was correctly computed, thus allowing one to prove homomorphic evaluation of unbounded depth. However, proving the TFHE bootstrapping procedure, which already takes  $\sim 10$ ms to perform honestly, takes > 5 seconds (per circuit gate).

ZFHE [83] proves in zero-knowledge that it correctly evaluated an FHE payload circuit. Their primary goal is to hide private server inputs from the client, and their proofs are linear in the circuit size (not succinct). Despite sacrificing succinctness, ZFHE still has at least <sup>10</sup> a two order of magnitude overhead over honest execution of the FHE payload computation.

#### 1.4 Technical Overview

Blind Interactive Oracle Proofs. We first recap the blind interactive oracle proof framework from [36], which is essential to understanding our design choices. In a public-coin IOP, the prover sends vector oracles to a verifier who replies with random challenges. Modern SNARKs are built from IOPs following a two step process. First, the vector oracles are instantiated with some vector commitment scheme (e.g. by using Merkle trees, or by sending the entire vector itself as per Remark 2.1). This results in a public-coin interactive proof (IP). Then interaction is removed via the Fiat-Shamir heuristic, i.e., replacing verifier challenges with hashes of the transcript. The key observation in [36] is that a VCoED scheme need not homomorphically evaluate the entire SNARK prover (which includes hashing). Instead, the server only needs to homomorphically evaluate the underlying IOP prover circuit.

Vector commitments can be computed *outside* of the FHE context; for instance, one can construct a Merkle tree by treating each ciphertext as a leaf or a block of data to be committed. Similarly, the Fiat-Shamir verifier challenges can be generated externally by hashing the ciphertexts of the running transcript. The intuition is that hashing of these ciphertexts (instead of the plaintexts they encode) remains adequately binding. Thus, this retains the temporal ordering that Fiat-Shamir enforces on the IP execution without requiring expensive homomorphic evaluation of hash functions.

Furthermore, the above implies that the verifier's challenges can be treated as *scalar inputs* to the homomorphic evaluation of the the IOP prover's circuit. This is a significant improvement, as it allows some of the prover's circuit to be evaluated via cheap scalar-ciphertext operations, rather than ciphertext-ciphertext operations that are costly in runtime and noise budget. Furthermore, even though the IOP prover executes multiple rounds, each logically dependent on the previous ones, these rounds do not add up in terms of multiplicative depth, because the hashing of transcript

<sup>&</sup>lt;sup>10</sup>Note that the extended version of [83] contains corrected benchmarks.

ciphertexts into Fiat-Shamir challenge scalars effectively resets their FHE multiplicative level. 11

The powerful consequence is that we need only design a *public-coin IOP* with an FHE-friendly prover, as compilation to a blind SNARG adds negligible overhead.

Core Insight: GKR is the right tool. Our core insight is that the GKR IOP is uniquely well-suited for homomorphic evaluation. Most other IOP choices require a polynomial commitment (PC) under FHE, where the total degree of the polynomial is linear in the circuit size; such PCs force the server to sacrifice either constant multiplicative depth or quasi-linear runtime (from NTTs). Furthermore, mitigating these costs leads to sacrificing the SIMD parallelism of payload circuit execution, as discussed in Section 1.1.

In contrast, the GKR protocol's IOP prover consists of only two tasks: evaluating multilinear polynomials and computing sumcheck round polynomials.<sup>12</sup> Both of these tasks can be very FHE-friendly, without a transformation that incurs a super-logarithmic blowup to the size of the prover circuit to achieve constant multiplicative depth. Multilinear evaluation reduces to a simple inner product, and the sumcheck prover circuit is discussed below. Computing the whole GKR proof then reduces to performing multiple rounds of this form, and as discussed above, the total multiplicative depth needed to homomorphically evaluate all rounds equals that of a single round.

FHE-Friendly GKR Sumchecks. The classic, linear-time sumcheck algorithm [28, 73] reuses work from previous rounds. This dependency gives it an  $\mathcal{O}(\mu)$  multiplicative depth (where  $\mu$  is the number of rounds), which is exactly the kind of super-constant depth we are trying to avoid. However, a different, quasi-linear time sumcheck algorithm from [27] offers a crucial work-depth trade-off. In this algorithm, the prover computes each of the  $\mu$  round polynomials from scratch, without reusing work. While this is less efficient in the plaintext setting (total work is quasi-linear, not linear), its circuit boasts an O(1) multiplicative depth. The observation that Spartan sumcheck instances can be computed in low multiplicative depth was used in [81]. In our work, we optimize the prover circuit for GKR sumcheck instances (which are more complicated than those from Spartan), carefully tailoring them to be efficient for the blind prover, and attain a multiplicative depth only 2.5.

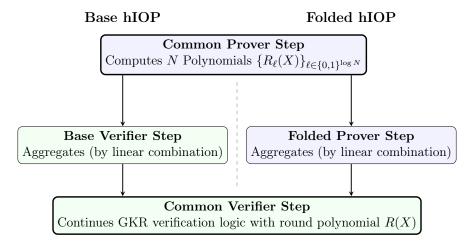

For a d-layer circuit, the GKR protocol invokes sumcheck d times to reduce a claim about the output layer to one about input layer.<sup>13</sup> The ith sumcheck is taken over a  $\mu_i$ -variate polynomial for some  $\mu_i > \log N$ . In Section 4, we describe two variants of the GKR IOP, which we term base and folded IOPs. The folded IOP is conceptually simple; it completes all  $\mu_i$  rounds of each sumcheck exactly as prescribed, and requires multiplicative depth 2.5. However, the base IOP is tailored to be maximally FHE-friendly, doing so in two key ways. First, it terminates each sumcheck  $\log N$  rounds early, which saves the server some FHE operations. Second, it skips the final steps performed by the folded IOP prover, which can include evaluating a  $\log N$ -variate multilinear polynomial (which requires one additional level of multiplication). The consequence of these choices is that the base IOP prover achieves a multiplicative depth of only 1.5 at the cost of having the base IOP verifier receiving larger proofs and finishing the computations the prover did not complete.<sup>14</sup>

<sup>&</sup>lt;sup>11</sup>The actual homomorphic evaluation of the prover rounds remains temporally ordered by the need to compute the Fiat-Shamir challenges in sequence.

<sup>&</sup>lt;sup>12</sup>See Section 2.7 for details on the [64] sumcheck protocol.

<sup>&</sup>lt;sup>13</sup>These sumchecks are made more efficient by exploiting the "data-parallel" circuit structure [73] present in payload circuits designed for BGV evaluation (see Section 3.1.3).

$<sup>^{14}</sup>$ One can think of the base IOP prover as spawning N threads to compute each round message, but rather than joining the results, it sends each thread's result directly to the base IOP verifier who locally performs aggregation. Aggregation often entails an evaluation of a multilinear extension of the results at a random evaluation point, though occassionally only requires computing a sum of N terms. The "folded" descriptor refers to how a folded prover "folds" the results of its N threads before presenting it to the verifier.

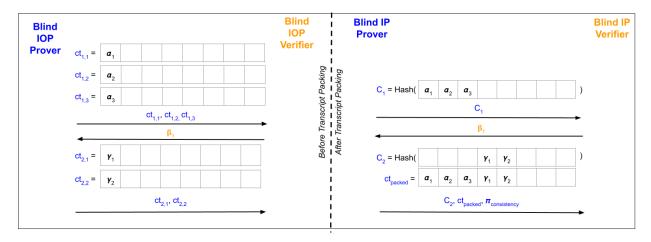

Figure 2: Transcript Packing compilation for a two-round protocol with SIMD capacity N=8. The naive Blind IOP prover sends 5 ciphertexts (40 slots) to convey only 5 useful values. The compiled Blind IP prover aggregates these into a single packed ciphertext (8 slots), supplemented by hash digests and a SNARK proving consistency between the packed ciphertext and the committed preimages.

Challenge: Succinct Proof Sizes. In each round  $i \in [r]$ , our folded BIOP prover sends an oracle to a length  $m_i$ -vector of ciphertexts. When using a plaintext space of roughly  $2^{16}$  targeting  $\lambda = 100$  bits of security, this vector consists concretely of  $m_i \approx 24$  ciphertexts. The folded verifier needs to learn  $m_i$  of the  $m_i \cdot N$  communicated field elements - one from each ciphertext. The natural choice would be to compile our folded IOP with the trivial vector commitment scheme, as is typical in GKR-based SNARGs. However, we would then be sending  $m_i$  ciphertexts in every round, each of size 7N bytes.

For circuits with d=32 layers,  $n=2^{20}$  gates, and  $N=2^{14}$  SIMD slots, there are  $r\approx 1500$  total rounds, resulting in 252N kilobytes, or 4 GB. This is unacceptable, especially in the extreme case where the payload circuit uses only 1 active slot and we do not have multiple instances to batch.

**Solution:** Transcript Packing. We instead develop a new Blind IOP to Blind IP compiler. We outline the compiler (we consider only the folded Blind IOP for exposition sake), and a full treatment can be found in Section 5.2.

Our first step is to reduce space consumption in each round. For round  $i \in [r]$ , let  $m_i$  denote the number of field elements sent by the GKR prover. It would be inefficient for a blind prover to send  $m_i$  ciphertexts in round i, as it wastes  $m_i \cdot (N-1)$  slots. With a lightweight "flattening" procedure (via rotation and addition), we consolidate the  $m_i$  ciphertexts into a *single* ciphertext. However, this approach still wastes  $N - m_i$  slots *per round*.

Ideally, we would pack all round information into a handful of packed ciphertexts. However, it is not obvious a priori how to do so. Such ciphertexts would need to contain prover messages across multiple rounds, but the soundness analysis of IPs require that the verifier observe round i messages before sending challenges that are used to compute the round i+1 messages. Our solution is to succinctly commit to unpacked ciphertexts in each round, each using unique global slot indices. In the final round, the prover sends just enough "packed ciphertexts" to contain  $m := \sum_{i=1}^{r} m_i$  slots of information, consistent with the committed unpacked ciphertexts, along with a SNARK proof of this consistency. Intuitively, these (relaxed) commitments bind the prover to underlying plaintext slots, thereby preserving IP soundness. As we discuss in Section 5.2, this "proof of packing" adds negligible overhead to proof size and is tractable for the prover. Application of transcript packing compilation from a blind IOP to a blind IP is depicted in Fig. 2.

When our folded Blind IOP is compiled into a Blind IP using this transcript packing, the

resulting VCoED scheme (after further Fiat-Shamir compilation into a Blind SNARG) is called Laminate<sub>fold</sub>. For a payload circuit with d=32 layers,  $n=2^{20}$  gates,  $N=2^{14}$  slots, and plaintext modulus  $q=2^{16}+1$ , Laminate<sub>fold</sub> achieves proof sizes of 270 kilobytes. When the payload circuit is evaluating  $B=2^{14}$  disjoint instances to fully utilize the SIMD capacity of the payload circuit, this implies a per instance proof size of only 16.5 bytes, in stark contrast to [81]'s per-instance proof size of 60 megabytes.

Limitations. We discuss two limitations of our framework. First, our blind proof framework is inherently designated verifier: only a holder of the secret key can verify a blind proof. This contrasts with "SNARK-over-FHE" approaches, where the server proves statements about ciphertexts that anyone can verify. However, as demonstrated in [36], designated-verifier blind proofs can be lifted to public verifiability via proof composition. Second, the "FHE-over-SNARK" paradigm exhibits a fundamental one-bit leakage if the adversary observes the verification result. While this is an inherent trade-off, the alternative SNARK-over-FHE paradigm faces its own security challenges: as discussed in Remark 2.10, our approach offers resistance against known IND-CPA-D key-recovery attacks.

### 1.5 Summary of Evaluation

#### 1.5.1 Comparisons with Prior Works

The full VCoED scheme incurs the following costs. For simplicity, we focus on the performance of Laminate<sub>fold</sub> (unless otherwise noted), which is a version that focuses on *minimizing the proof size*, and compare all our variants in detail in Section 6 (which may provide better server runtime and lower multiplicative depth).

Homomorphically evaluating the blind SNARG. Following prior works [81, 36], we provide an estimation of the runtime of our construction using detailed operation counts and microbenchmarks. Concretely, for a circuit with  $2^{20}$  gates as in [81, 36], the runtime<sup>15</sup> for evaluating the blind SNARG is  $\sim 495 \times$  faster than [81] and  $\sim 2012 \times$  faster than [36] when fully utilizing our batching capacity (evaluating  $2^{14}$  independent instances). Given just  $2^{7}$  instances, we still outperform by  $\sim 3.9 \times$  and  $\sim 15.7 \times$  respectively. Moreover, these advantages increase as circuit size grows, since the servers in prior work require more than quasi-linear FHE operations to homomorphically evaluate the blind SNARG under FHE in constant multiplicative depth (due to NTT-based polynomial commitments, see Section 1.1).

**Proof size.** Laminate's proof size is only  $\sim 0.27\,\mathrm{MB}$  regardless of the number of instances batched together. For a single instance, this is  $> 215\times$  smaller than prior work (60 MB in [81]). For  $2^{14}$  instances, it is  $> 3,500,000\times$  smaller.

Homomorphic payload computation. Because Laminate allows parallel execution of independent instances using all  $N = 2^{14}$  SIMD slots, it attains a corresponding performance advantage:  $2^{14} \times$  more throughput in homomorphic evaluation of the payload circuits, compared to the single-slot payload evaluation in [81, 36].

Input ciphertext blowup. Should prior schemes tune parameters to make their server perform quasi-linear (needed for larger circuits), then they must introduce an overhead of  $\Omega(\log n)$  multiplicative depth for evaluating the prover. This necessitates a noise budget increase (concretely: at least 200 extra bits), and thus larger input ciphertexts and correspondingly slower evaluation of the payload circuit. Laminate reduces this overhead to (depending on the variant) between 1.5 and 3.5 multiplicative levels (concretely, 50 to 120 bits of noise budget).

<sup>&</sup>lt;sup>15</sup>Via operation counts (see Remark 4.1) and microbenchmarks (see Section 6) as prior works.

For example, OMR [58] uses  $\sim 800$  bits of noise budget for honest evaluation; thus the ciphertext size overhead is between  $\sim 6.25\%$  and  $\sim 15\%$  with Laminate, compared to > 25% with prior schemes. This advantage further increases as the circuit size grows, since the multiplicative depth of our quasi-linear server circuit is always *constant*, unlike prior works.

Witness reduction. Lastly, our construction does not incur the potentially huge costs of witness reduction, which are inherent (albeit not accounted for) in prior work, as discussed in Section 1.1.

#### 1.5.2 Comparisons with Honest Payload Generation

We now compare our results to honest payload generation, where the circuit is homomorphically evaluated without any integrity proof. For a circuit with  $2^{20}$  gates, evaluation time varies with the circuit's topology, specifically the distribution of gate types (multiplications vs. additions) and the multiplicative levels at which they occur. Across all scenarios we have considered, honest evaluation ranges from 0.2 hours to 7.0 hours.

Compared to this honest evaluation, Laminate incurs as little as  $\sim 12\times$  overhead when the circuit is multiplication-heavy and most operations occur near the input layer. Across all tested settings, the overhead remains below  $370\times$ , with the worst case arising when the circuit is dominated by additions concentrated near the output layer. This cost includes the additional payload generation overhead incurred by the extra multiplicative depth required by Laminate.

### 2 Preliminaries

### 2.1 (Leveled) Homomorphic Encryption

A (leveled) homomorphic encryption (HE) scheme provides four algorithms: KeyGen, Enc, Dec, Eval. The Eval algorithm allows for public computation on encrypted data. Given a function f and ciphertexts  $\mathsf{ct}_i = \mathsf{Enc}(\mathsf{pk}, m_i)$ , Eval computes  $\mathsf{ct}' \leftarrow \mathsf{Eval}(\mathsf{evk}, f, \mathsf{ct}_1, \ldots, \mathsf{ct}_w)$  such that  $\mathsf{Dec}(\mathsf{sk}, \mathsf{ct}') = f(m_1, \ldots, m_w)$ . We use leveled HE, which supports circuits up to a predetermined depth MAXDEPTH without a costly bootstrapping operation. We denote semantic security by IND-CPA.

**Notation.** We say that a ciphertext ct encrypts a plaintext x if x = Dec(sk, ct) where sk is the client's decryption key, which will usually be implicit.

Let  $\mathbb{F}_p$  be the (base) plaintext space for some finite field order p. For plaintexts  $\vec{x} \in \mathbb{F}_p^k$ , let  $\mathsf{ct}[\vec{x}] = (\mathsf{ct}[\vec{x}_1], \dots, \mathsf{ct}[\vec{x}_k])$  denote a vector of ciphertexts encrypting  $\vec{x}$ . For any two vectors of ciphertext  $\vec{\mathsf{ct}}_1, \vec{\mathsf{ct}}_2$  of size k, we use  $\vec{\mathsf{ct}}_1 \times \vec{\mathsf{ct}}_2$  to denote the homomorphic multiplication  $\mathsf{Eval}(\mathsf{pp}, \mathsf{evk}, \times, \vec{\mathsf{ct}}_1[i], \vec{\mathsf{ct}}_2[i])_{i \in [k]}$ . We similarly define  $\vec{x} \times \vec{\mathsf{ct}}$  for plaintext vector  $\vec{x}$  and ciphertext vector  $\vec{\mathsf{ct}}$ . Homomorphic additions (+) are defined analogously.

We also consider an extended plaintext space  $\mathbb{F}_{p^R}$  for some R>1. The extended ciphertext (ect) encrypting an extended plaintext  $x\in\mathbb{F}_{p^R}$  consists of R ciphertexts. For  $\vec{x}\in\mathbb{F}_{p^R}^k$ , let  $\mathsf{ect}[\vec{x}]=(\mathsf{ect}[\vec{x}_1],\ldots,\mathsf{ect}[\vec{x}_k])$  denote a vector encrypting  $\vec{x}$ , where  $\mathsf{ect}[\vec{x}_i]$  ( $i\in[k]$ ) consists of R ciphertexts. The homomorphic operations  $\times$  and + are defined analogously; if any of their inputs is an extended plaintext in  $\mathbb{F}_{p^R}$ , or the encryption of such a plaintext, then the operation is done in  $\mathbb{F}_{p^R}$ ; otherwise it is  $\mathbb{F}_p$ .

We use  $depth(ct[\cdot])$  to denote the maximum depth of the circuit over which a ciphertext can be evaluated (and in particular  $depth(ct[\cdot]) \leq MAXDEPTH$  for all ciphertexts).

**Leveled HE and FHE.** Bootstrapping [41] can transform leveled HE (LHE) to FHE. In all existing FHE constructions, the input ciphertexts have some inherent initial noise, which accumulates with each level of ciphertext evaluation. Bootstrapping is a method that is used to reduce the

accumulated noise in ciphertexts back to some initial level. Unfortunately, all the existing methods of bootstrapping are very costly [50, 39, 62, 66, 61]. Thus, in practice, most applications only use the leveled version of HE, where the depth MAXDEPTH of the computation is bounded, thereby the focus of this work.

### 2.2 Indexed Languages and Proof Systems

Indexed Languages. We are concerned with indexed languages  $\mathcal{L} = \{\mathcal{L}_i\}$ , where an index i (e.g., a circuit) defines a specific language  $\mathcal{L}_i$  (e.g., valid input-output pairs). We use preprocessing proof systems where i is preprocessed into a short encoding e[i]. A verifier can then use e[i] to check proofs in time sublinear in the size of i.

Interactive Oracle Proofs. Our work builds on public-coin *Holographic Interactive Oracle Proofs* (pc-hIOPs) for indexed languages [6, 24]. In each round, the prover sends the verifier a vector oracle and the verifier replies with a uniformly random message. At the end of the protocol, the verifier can query the vector oracles sent by the prover and make a decision to accept or reject the proof.

**IOP to SNARG compilation.** These information-theoretic protocols can be compiled into Succinct Non-interactive Arguments (SNARGs) in two steps. First, by using a Vector Commitment Scheme (VCS) to instantiate the vector oracles sent by the IOP prover, we compile an IOP into an interactive proof. Then, after applying the Fiat-Shamir transformation in the Random Oracle Model (ROM) [33], the protocol is non-interactive.

Remark 2.1 (The Trivial VCS). When the IOP prover sends vector oracles whose underlying vectors are singletons (or consist of a small handful of elements), a desirable choice is the "trivial" VCS where the commitment is the vector itself. In the trivial VCS, openings are a no-op. The verifier, having received the entire vector  $m_j$  as the "commitment," simply reads the entry at index q to verify the "opening."

### 2.3 Blind Indexed Language

Our goal is not just to prove statements about public data, but to prove statements about encrypted data. To do this, we introduce a homomorphic encryption (HE) scheme  $\mathcal{E}$ . We now formalize the problem we want to solve: proving membership in an indexed language, where both the index and the instance are "blinded" by encryption.

**Definition 2.2** ([36]). For a given HE scheme  $\mathcal{E} = (\text{KeyGen}, \text{Enc}, \text{Dec}, \text{Eval})$ , and indexed language  $\mathcal{L}$ , we define the *indexed blind language*  $\mathcal{E}[\mathcal{L}]$  as:

$$\mathcal{E}[\mathcal{L}] = \{(i'; x') = ((i, \mathsf{sk}); \mathsf{ct}[x]) : \mathcal{E}.\mathsf{Dec}_{\mathsf{sk}}(\mathsf{ct}[x]) = x \in \mathcal{L}_i\}$$

For a fixed blind index i' = (i, sk), the blind language is  $\mathcal{E}[\mathcal{L}_{i'}] = \{x' : (i'; x') \in \mathcal{E}[\mathcal{L}]\}$ .

**Definition 2.3.** For a blind index i' = (i, sk), we refer to i as the *public index* (which is known to all parties) and sk as the *secret index* (which is known only to the verifier).

**Lemma 2.4** ([36]). If  $\mathcal{E}$  is an IND-CPA secure HE scheme, any PPT adversary has only negligible advantage in distinguishing the underlying  $x \in \mathcal{L}_i$  given a corresponding  $x' = \operatorname{ct}[x] \in \mathcal{E}[\mathcal{L}_{i'}]$ .

**Remark 2.5.** This is a slight simplification of the definition in [36]. Specifically, we allow the modify the index i' to include the secret key. Since we are building towards a designated-verifier VCoED scheme, it is okay for only the designated verifier to know the blind language  $\mathcal{E}[\mathcal{L}_{i'}]$ .

### 2.4 Public-Coin Blind Holographic Interactive Oracle Proofs

We first define the *interactive* version of a proof system for this blind language. A Blind hOIP (BhIOP) is conceptually a standard hIOP "lifted" into the encrypted domain using HE. The prover receives an evaluation key evk and homomorphically evaluates the prover's algorithm under encryption. The BhIOP verifier uses the secret key sk to simulate the hIOP verifier by decrypting only the queried oracle entries.

**Definition 2.6** (Public-Coin Blind hIOP (BhIOP) [36]). For a given HE scheme  $\mathcal{E}$  and public-coin hIOP  $\pi$  for  $\mathcal{L}$ , a public-coin blind hIOP  $\mathcal{E}[\pi] = (\mathsf{Setup}, \mathsf{P}, \mathsf{V})$  for the indexed blind language  $\mathcal{E}[\mathcal{L}]$  includes the following PPT algorithms:

- $\mathcal{E}[\pi]$ . Setup $(1^{\lambda}, i)$ : For a public index i, this algorithm:

- Generates (sk, evk)  $\leftarrow \mathcal{E}$ .KeyGen(1 $^{\lambda}$ ).

- Generates the plaintext encoding  $e[i] \leftarrow \pi.\mathsf{Ind}(i)$ .

- Outputs (evk, (sk, e[i])). The blind index is now i' = (i, sk).

- $\mathcal{E}[\pi].\mathsf{P}_{\mathsf{evk}}(i,x')$ : The prover, given i, the encrypted instance  $x' = \mathsf{ct}[x]$ , and  $\mathsf{evk}$ , interacts with the verifier. In round  $j \in [\mu]$ , it receives the "transcript so far"  $\mathsf{tr}'$  (which contains encrypted messages) and computes the next round message by homomorphically evaluating the plaintext prover  $\pi.\mathsf{P}_j$ :

$$\mathsf{ct}[m_i] \leftarrow \mathcal{E}.\mathsf{Eval}_{\mathsf{evk}}(\pi.\mathsf{P}_i,(i,\mathsf{ct}[x],\mathsf{tr}'))$$

(Here, tr' is decrypted and re-encrypted as needed inside Eval.)

- $\mathcal{E}[\pi]$ . $V_{sk}(e[i], x')$ : The verifier, given e[i],  $x' = \mathsf{ct}[x]$ , and  $\mathsf{sk}$ , interacts with the prover.

- Rounds  $j = 1 \dots \mu$  (Message Rounds):  $\mathcal{E}[\pi]$ . V receives the ciphertext oracle  $\mathsf{ct}[m_j]$  and stores it in its transcript  $\mathsf{tr}'$ . It then returns a fresh random (scalar) challenge  $\rho_j$ .

- Round  $\mu + 1$  (Decision Round):  $\mathcal{E}[\pi]$ .V first computes  $x := \mathcal{E}.\mathsf{Dec}_{\mathsf{sk}}(x')$ . It then executes the algorithm of the plaintext verifier  $\pi.V$ , providing it with x. When the  $\pi.V$  algorithm needs to make a query at a location q:

- \* To the index e[i]:  $\mathcal{E}[\pi]$ . V reads e[i][q] from its input and returns it.

- \* To a prover oracle  $m_j$ :  $\mathcal{E}[\pi]$ . V retrieves its stored ciphertext oracle  $\mathsf{ct}[m_j]$ , computes  $v := \mathcal{E}.\mathsf{Dec}_{\mathsf{sk}}(\mathsf{ct}[m_j][q])$ , and returns the plaintext value v.

$\mathcal{E}[\pi]$ . V then outputs the final accept/reject decision of  $\pi.V$ .

**Remark 2.7.** We again modify the original definition from [36] for simplicity. This definition is specific to the *public-coin* setting, which is the only setting of practical interest.

### 2.5 The Blind SNARG Compilation

We compile the public-coin BhIOP from Section 2.4 into a non-interactive blind SNARG using the compilation described in Section 2.2. The VCS chosen for this compilation must support committing to a vector of *ciphertexts* and allow the verifier to request opening proofs to specific positions of the committed vector. The trivial VCS (see Remark 2.1) is a valid choice.

Letting  $\llbracket \rho \rrbracket$  denote a random oracle, the blind SNARG prover computes the jth verifier challenge as  $\rho_j := \llbracket \rho \rrbracket$  (tr), where the transcript tr contains all public data, including the index i, the encrypted instance x', and all ciphertext messages  $\mathsf{ct}[m_k]$  sent so far.

The verifier (who holds sk) runs the non-interactive protocol, decrypts the necessary queries from the proof ciphertexts, and runs the plaintext verifier's logic to accept or reject.

Remark 2.8 (Designated Verifier blind SNARGs). The blind SNARGs described in this manuscript are designated-verifier SNARGs, as the secret key sk is needed for verification. This is shared across all prior works that follow the FHE-over-SNARK paradigm [38, 4, 36, 81].

Remark 2.9 (One-bit leakage for FHE-over-SNARK). As mentioned in prior works [4, 36, 81], there is a one-bit leakage of the payload in the FHE-over-SNARK paradigm. For example, an adversary could replace one bit of the payload with the value 1 and follow the rest of the protocol honestly. The blind proof would pass the check if the replaced bit is 1 and fail otherwise. With access to the verification result, the adversary learns this bit of payload. This is inherent for the FHE-over-SNARK paradigm, since proofs are generated with respect to underlying plaintexts. The SNARK-over-FHE avoids this since the proof attests that each intermediate *ciphertext* was properly generated. On the other hand, the difference in the statements being proven give an advantage to the FHE-over-SNARK paradigm in other settings, as discussed in Remark 2.10.

Remark 2.10 (IND-CPA-D of FHE). While our scheme (or in general any SNARK-over-FHE and FHE-over-SNARK schemes) guarantees integrity for *correctness*, it does not *a priori* rule out a security leakage (e.g., payload leakage) if decrypted plaintexts are leaked (even if all the ciphertexts are guaranteed to be correctly formed, captured by the IND-CPA-D model [54, 55, 1, 8, 18] for FHE). In other words, *even though* the FHE-over-SNARK or SNARK-over-FHE paradigms guarantee that the evaluation process is correct, FHE schemes might still be insecure in the presence of a decryption oracle.

It is worth noting that the FHE-over-SNARK paradigm has an advantage over the SNARK-over-FHE approach in this setting. Specifically, for "exact FHE" schemes such as BGV, BFV, FHEW, and TFHE [15, 14, 32, 31, 25], to our knowledge, all known attacks on their IND-CPA-D security exploit the fact that accumulated errors and bootstrapping (or the accumulated noise) can alter the underlying plaintexts during decryption [22, 19, 63]. Such plaintext changes may occur even when the ciphertext evaluations are computed correctly, allowing these attacks to bypass the SNARK-over-FHE paradigm. Intuitively, FHE-over-SNARK can prevent this attack, since the decrypted SNARK proves a statement about the plaintexts directly. We leave a formal exploration of this observation as future work.

### 2.6 Multilinear Polynomials and Multilinear Extensions

**Definition 2.11.** A multilinear polynomial  $f(X_1, \ldots, X_n) \in \mathbb{F}[X_1, \ldots, X_n]$  is linear in each variable.

Fact 2.12. A multilinear polynomial on n variables can be uniquely defined by its evaluations over the Boolean Hypercube domain  $\{0,1\}^n$ . As a corollary, any function  $h:\{0,1\}^n \to \mathbb{F}$  has a unique multilinear extension (MLE)  $\tilde{h}:\mathbb{F}^n \to \mathbb{F}$  such that  $\forall \vec{v} \in \{0,1\}^n$ ,  $f(\vec{v}) = \tilde{h}(\vec{v})$ .

The equality multilinear polynomial. We define  $\tilde{\mathsf{eq}}_n(X_1,\ldots,X_n,Y_1,\ldots,Y_n)$  as the multilinear extension of the function  $\mathsf{eq}:\{0,1\}^n\times\{0,1\}^n\to\{0,1\}\subseteq\mathbb{F}$  defined like so:

$$eq(X_1, \dots, X_n, Y_1, \dots, Y_n) = \begin{cases} 1 \text{ if } X_i = Y_i \text{ for all } i \in [n], \\ 0 \text{ otherwise.} \end{cases}$$

The multilinear extension  $\tilde{\mathsf{eq}}_n \in \mathbb{F}[X_1, \dots, Y_n]$  is defined like so:

$$\tilde{\mathsf{eq}}_n[X_1,\ldots,X_n,Y_1,\ldots,Y_n] = \prod_{i=1}^n (X_i Y_i + (1-X_i)(1-Y_i))$$

Note that this is multilinear and its Boolean hypercube evaluations agree with the function eq.

**Arbitrary Multilinear Extensions.** Fix an arbitrary list of values  $(a_{\vec{v}})_{\vec{v} \in \{0,1\}^n}$  and let  $h: \{0,1\}^n \to \mathbb{F}$  be the function such that  $h(\vec{v}) = a_{\vec{v}} \in \mathbb{F}$  for all  $v \in \{0,1\}^n$ . We express the multilinear extension of h, denoted  $\tilde{h}$ , via Lagrange Interpolation.

$$\tilde{h}(X_1, X_1, \dots, X_n) = \sum_{\vec{v} \in \{0,1\}^n} a_{\vec{v}} \cdot \tilde{\mathsf{eq}}_n(X_1, X_2, \dots, X_n, v_1, v_2, \dots, v_n)$$

(1)

**Definition 2.13.** We call  $(a_{\vec{v}})_{\vec{v} \in \{0,1\}^n}$  the Lagrange Coefficients of  $\tilde{h}$ .

**Evaluation in Extension Field.** Let  $\mathbb{E}$  be an extension field of  $\mathbb{F}$ . It is well defined to view  $\tilde{h}$  as a multilinear polynomial defined over  $\mathbb{E}$ , and thus we can evaluate it at any point  $\vec{\gamma} \in \mathbb{E}^n$ . As seen in Equation (1), we can evaluate  $\tilde{h}$  at  $\vec{\gamma}$  by evaluating each Lagrange Basis polynomial  $L_{\vec{v}}(X_1,\ldots,X_n):=\tilde{\text{eq}}(X_1,\ldots,X_n,\vec{v})$  for  $\vec{v}\in\{0,1\}^n$  at  $\vec{X}=\vec{\gamma}$  and taking an inner product with the Lagrange coefficients.

### 2.7 Multivariate Sumcheck Protocol

We briefly recall the multivariate sumcheck protocol from [64] as used by modern proof systems. Let  $\mathbb{F}$  be a field, and let  $\mathbb{E}$  be an extension field of  $\mathbb{F}$  that is cryptographically large, i.e.  $|\mathbb{E}| \geq 2^{\lambda}$  for security parameter  $\lambda$ .

The prover has access to a multivariate polynomial  $f(X_0, \ldots, X_{\mu-1}) \in \mathbb{F}[X_0, \ldots, X_{\mu-1}]^{\leq d}$  of maximium individual degree d. (Typically d is a small constant, like 3.) The verifier has oracle access to f. The prover wants to convince a distrustful verifier that

$$\sum_{x_0,\dots,x_{\mu-1}\in\{0,1\}} f(x_0,\dots,x_{\mu-1}) = s_0 \in \mathbb{F}.$$

in such a way that the verifier need only evaluate f one time (which requires  $2^{\mu}$  times without the prover, since the verifier needs to compute the entire procedure itself).

This takes place over  $\mu$  rounds. In round  $i \in \{0, \dots, \mu - 1\}$ , the prover reduces a claim about the sum of  $2^{\mu - i}$  values to a claim about the sum of  $2^{\mu - i - 1}$  values. The protocol proceeds like so. That is, the initial claim is that  $\sum_{x_0, \dots, x_{\mu - 1} \in \{0, 1\}} f(x_0, \dots, x_{\mu - 1}) = s_0$ . Then in round 0, the prover sends a degree d univariate round polynomial  $R_0(X) \in \mathbb{F}[X]^{\leq d}$  claiming that

$$R_0(X) = \sum_{x_1, \dots, x_{\mu-1} \in \{0,1\}} f(X, x_1, \dots, x_{\mu-1})$$

If the prover is honest, then  $R_0(0) + R_0(1) = \sum_{x_0, \dots, x_{\mu-1} \in \{0,1\}} f(x_0, \dots, x_{\mu-1})$ . So, the verifier checks that  $R_0(0) + R_0(1) = s_0$ . Next, the verifier samples a uniform random challenge  $\gamma_0 \stackrel{\$}{\leftarrow} \mathbb{E}$  and evaluates  $s_1 := R_0(\gamma_0)$ . The next round claim is that  $\sum_{x_1, \dots, x_{\mu-1} \in \{0,1\}} f(\gamma_0, x_2, \dots, x_n) = s_1$ . This process repeats in round  $1, \dots, n-1$  until we are left with a final round claim  $f(\gamma_0, \dots, \gamma_{n-1}) = s_n$

Completeness Intuition If the initial claim is true and the prover follows the protocol, then all subsequent round claims will be true.

**Soundness Intuition** Suppose in round i the current claim is false. The dishonest prover has two choices. If it sends the "real" round polynomial  $R_i(X)$  such that

$$R_i(X) = \sum_{x_{i+1},\dots,x_{\mu-1} \in \{0,1\}} f(\gamma_0,\dots,\gamma_{i-1},X,x_{i+1},\dots,x_{\mu-1})$$

then  $R_i(0) + R_i(1) \neq s_i$ , and the verifier will reject. If it sends a fake round polynomial, then  $R_i(X) \neq \sum_{x_{i+1},\dots,x_{\mu-1}\in\{0,1\}} f(\gamma_0,\dots,\gamma_{i-1},X,x_{i+1},\dots,x_{\mu-1})$ , so with probability at least  $1 - \frac{d}{|\mathbb{E}|}$ ,  $R_i(\gamma_i) \neq \sum_{x_{i+1},\dots,x_{\mu-1}\in\{0,1\}} f(\gamma_0,\dots,\gamma_{i-1},\gamma_i,x_{i+1},\dots,x_{\mu-1})$ , in which case the next round claim will also be false. So, the dishonest prover has  $\mu$  rounds to turn a false claim into a true claim, but in each round, the probability of doing so is at most  $\frac{d}{|\mathbb{E}|}$ . By Union Bound, a cheating prover fools the verifier with probability at most  $\frac{d\mu}{\mathbb{E}}$ .

Remark 2.14 (Simple optimization: omit one round polynomial evaluation). Typically, the prover specifies a degree d round polynomial with d+1 evaluations (e.g.  $R(0), \ldots, R(d)$  if the field has characteristic more than d). However, since the verifier is going to check R(0)+R(1)=s, the prover can save time and omit evaluating R(1), as the verifier can simply deduce it. Thus, we will assume that the prover uses d evaluations (e.g.  $R(0), R(2), \ldots, R(d)$ ) to specify degree d round polynomials.

## 3 Requisite hIOP and HE Schemes

We review the GKR protocol (specifically the refinement of [27] described in [74]) and the BGV/BFV FHE scheme.

### 3.1 GKR Protocol

Let Ckt be a depth d layered fan-in-two arithmetic circuit over field  $\mathbb{F}_q$ . By convention, we say  $L_0$  is the list of output wires,  $L_d$  is the list of input wires, and  $L_i$  is the list of wires in layer i. The layered requirement states that every wire in  $L_i$  is the output of an ADD or MUL gate applied to two wires in  $L_{i+1}$ . The GKR protocol describes how a prover P convinces verifier V of membership in the language

$$L_{\mathsf{Ckt}} = \{(\mathsf{in}, \mathsf{out}) \mid \mathsf{Ckt}(\mathsf{in}) = \mathsf{out}\}$$

with perfect completeness and negligible soundness error.

Formally, the GKR protocol can be described as a public-coin holographic Interactive (Oracle) Proof System  $HOL = (\mathbf{I}, \mathbf{P}, \mathbf{V})$ . The indexer  $\mathbf{I}$  processes  $\mathsf{Ckt}$  in an offline phase as follows.

For each layer  $j \in \{0, ..., d\}$ , it computes and stores  $s_j := \log_2(|L_j|).^{16}$  Then, for each layer  $j \in \{0, ..., d-1\}$ , it computes gate indicator functions  $\mathsf{add}_j, \mathsf{mul}_j : \{0, 1\}^{s_j} \times \{0, 1\}^{2s_{j+1}}$ :

$$\begin{aligned} \operatorname{add}_j(g,x,y) &= \begin{cases} 1 & \text{if } L_j[g] = L_{j+1}[x] + L_{j+1}[y], \\ 0 & \text{otherwise}. \end{cases} \\ \operatorname{mul}_i(g,x,y) &= \begin{cases} 1 & \text{if } L_j[g] = L_{j+1}[x] \cdot L_{j+1}[y], \\ 0 & \text{otherwise}. \end{cases} \end{aligned}$$

Using this, indexer I creates 2d commitments to multilinear extensions  $\tilde{\mathsf{add}}_j, \tilde{\mathsf{mul}}_j$  for all  $j \in \{0, \dots, d-1\}$ . The index i stores the  $s_j$ 's (log size of each layer) and the  $\mathsf{add}_j, \mathsf{mul}_j$  indicator

<sup>&</sup>lt;sup>16</sup>For ease of exposition, we will assume all layers have power-of-two many wires. If this is not the case, one can pad with dummy zero wires.

#### **GKR** Online Phase

- 1. **Initial Claim:** The protocol begins with the prover's initial claim that the circuit output matches the provided output:  $L_0 \stackrel{?}{=} \text{out}$ .

- 2. Output Randomization: The verifier V samples a random challenge  $\gamma \in (\mathbb{F}_{q^R})^{s_0}$  and sends it to the prover P. The claim is updated to be an evaluation of the multilinear extension:

$$\tilde{L}_0(\gamma) \stackrel{?}{=} \tilde{\mathsf{out}}(\gamma)$$

By the Schwartz-Zippel lemma, this step incurs a soundness loss of at most  $\frac{s_0}{|a^R|}$ .

- 3. Layer Reduction Loop: For each layer  $i = 0, \dots, d-1$ :

- P and V engage in a  $2s_{i+1} + 1$  round "layer reduction" subroutine.

- This subroutine reduces the claim about  $\tilde{L}_i$  (from the previous step) to a new claim of the form  $\tilde{L}_{i+1}(r_a) + \alpha \tilde{L}_{i+1}(r_b) \stackrel{?}{=} v$  for some  $r_a, r_b, \alpha, v$  derived during the subroutine.

- This reduction step incurs a soundness loss of  $\frac{8s_{i+1}+1}{q^R}$ .

- 4. **Final Check:** After the loop finishes (at i = d 1), the verifier holds a final claim about the input layer  $L_d$ :

$$\tilde{L}_d(r_a) + \alpha \tilde{L}_d(r_b) \stackrel{?}{=} v$$

The verifier can check this claim directly using the known circuit inputs in.

Figure 3: GKR Online Phase

functions. The encoded index e[i] stores the values  $\{s_j\}_{0 \leq j \leq d}$  and the multilinear commitments to  $\tilde{\mathsf{add}}_j, \tilde{\mathsf{mul}}_j$  for  $j \in \{0, \dots, d-1\}$ .

**Remark 3.1.** For the context of this paper, we will make a simplifying assumption that the verifier has access to  $\mathsf{add}_j, \mathsf{mul}_j$ , rather than commitments. We will justify this assumption further in Section 3.1.3.

After the offline phase, the prover and verifier engage in an interactive online phase, given in Figure 3 using the subroutines below.

#### 3.1.1 The Layer Reduction Subroutine

Recall from the high-level overview that at the beginning of round i (for  $i \in \{0, ..., d-1\}$ ), the verifier V holds a single claim about layer i. For i > 0, this claim is a batched evaluation:

$$\tilde{L}_i(\vec{r}_a) + \alpha \tilde{L}_i(\vec{r}_b) \stackrel{?}{=} v_i$$

where  $\vec{r}_a, \vec{r}_b$  and  $\alpha$  are challenges from the previous round's reduction. The layer reduction subroutine reduces this to a new, single claim about layer i + 1.

This reduction exploits the following fundamental identity, which relates the evaluation of  $\vec{L}_i$  at any point  $\vec{r}$  to a sum over all possible input wire pairs from layer i+1.

$$\tilde{L}_{i}(\vec{r}) = \sum_{\vec{x} \in \{0,1\}^{s_{i+1}}} \sum_{\vec{y} \in \{0,1\}^{s_{i+1}}} g^{(i)}(\vec{r}, \vec{x}, \vec{y})$$

(2)

$$\begin{split} \text{where } g^{(i)}(\vec{r}, \vec{x}, \vec{y}) := & \, \tilde{\mathsf{add}}_i(\vec{r}, \vec{x}, \vec{y}) \left( \tilde{L}_{i+1}(\vec{x}) + \tilde{L}_{i+1}(\vec{y}) \right) \\ & + \, \tilde{\mathsf{mul}}_i(\vec{r}, \vec{x}, \vec{y}) \left( \tilde{L}_{i+1}(\vec{x}) \cdot \tilde{L}_{i+1}(\vec{y}) \right) \end{split}$$

Applying this identity to the verifier's batched claim, we get:

$$\begin{aligned} v_i &\stackrel{?}{=} \tilde{L}_i(\vec{r}_a) + \alpha \tilde{L}_i(\vec{r}_b) \\ &= \sum_{\vec{x}, \vec{y}} g^{(i)}(\vec{r}_a, \vec{x}, \vec{y}) + \alpha \sum_{\vec{x}, \vec{y}} g^{(i)}(\vec{r}_b, \vec{x}, \vec{y}) \\ &= \sum_{\vec{x} \in \{0,1\}^{s_{i+1}}} \sum_{\vec{y} \in \{0,1\}^{s_{i+1}}} \left( g^{(i)}(\vec{r}_a, \vec{x}, \vec{y}) + \alpha g^{(i)}(\vec{r}_b, \vec{x}, \vec{y}) \right) \end{aligned}$$

Define the batched polynomial for the sumcheck as:

$$g_{\text{batch}}^{(i)}(\vec{x}, \vec{y}) := g^{(i)}(\vec{r}_a, \vec{x}, \vec{y}) + \alpha g^{(i)}(\vec{r}_b, \vec{x}, \vec{y})$$

(3)

The claim  $v_i$  is now equivalent to  $\sum_{\vec{x},\vec{y}} g_{\text{batch}}^{(i)}(\vec{x},\vec{y}) \stackrel{?}{=} v_i$ . The prover and verifier use the sumcheck protocol to verify this, as can be seen in Figure 4.

**Remark 3.2.** The first layer reduction (i=0) is a special case. The initial claim is  $\tilde{L}_0(\vec{\gamma}) \stackrel{?}{=} v_0$  (where  $v_0 = \tilde{\mathsf{out}}(\vec{\gamma})$ ). This can be seen as the general form  $\tilde{L}_0(\vec{r}_a) + \alpha \tilde{L}_0(\vec{r}_b) \stackrel{?}{=} v_0$  by setting  $\vec{r}_a = \vec{\gamma}$ ,  $\alpha = 0$ , and  $\vec{r}_b$  to an arbitrary vector (e.g.,  $\vec{0}$ ). The verifier's check in Step 2 simplifies accordingly, as  $v_a = \tilde{\mathsf{add}}_0(\vec{\gamma}, \vec{\rho}, \vec{\phi})$  and  $v_m = \tilde{\mathsf{mul}}_0(\vec{\gamma}, \vec{\rho}, \vec{\phi})$ .

**Theorem 3.3** ([27, 74]). The prover of the GKR refinement described in [27, 74] can be run in quasi-linear time with respect to the size of the circuit. Furthermore, the proof size and verifier time are linear in the number of GKR rounds.

**Remark 3.4.** Libra [78] describes a GKR variant that can be run in *linear* time, but the approach is not FHE-friendly.

#### 3.1.2 Round Complexity and Proof Size

The GKR protocol as described above is an r-round holographic IOP that is information-theoretically succinct, where  $r = \sum_{i=1}^{d} (2s_i + 1)$ . Instantiating the vector oracles with a trivial vector commitment scheme, we view GKR as a holographic IP. In each round, the prover sends at most three extension field elements. We give a convenient upper bound on GKR proof size, that depends only on the total number of gates n and the depth of the circuit d.

Claim 3.5. For a circuit of depth d and n gates, the number of GKR rounds is upper bounded by

$$d\left(2\log\left(\frac{n}{d}\right)+1\right)$$

*Proof.* The round complexity is defined as  $r = \sum_{i=1}^{d} (2s_i + 1)$ . Substituting  $s_i = \log S_i$ , we rewrite this sum as:

$$r = 2\sum_{i=1}^{d} \log S_i + d.$$

By definition, we know that  $\sum_{i=0}^{d} S_i = n$ , which implies  $\sum_{i=1}^{d} S_i \leq n$ . Since the logarithm function is concave, by Jensen's inequality, the term  $\sum_{i=1}^{d} \log S_i$  is maximized when all  $S_i$  are equal (i.e.,  $S_i = n/d$ ). Therefore:

$$\sum_{i=1}^{d} \log S_i \le d \cdot \log \left(\frac{n}{d}\right).$$

GKR Layer Reduction

$$(i \rightarrow i+1)$$

1. Sumcheck: P and V engage in a  $2s_{i+1}$ -round sumcheck protocol to prove the claim:

$$\sum_{\vec{x} \in \{0,1\}^{s_{i+1}}} \sum_{\vec{y} \in \{0,1\}^{s_{i+1}}} g_{\mathrm{batch}}^{(i)}\left(\vec{x}, \vec{y}\right) \stackrel{?}{=} v_i$$

At the end of the sumcheck, V has sampled random challenges  $\vec{\rho}, \vec{\phi} \in (\mathbb{E})^{s_{i+1}}$  and P has provided a final claimed value  $v_{\text{sum}}$ . The original claim is reduced to a new claim:

$$g_{\mathrm{batch}}^{(i)}(\vec{\rho}, \vec{\phi}) \stackrel{?}{=} v_{\mathsf{sum}}$$

2. Evaluate and Send: The verifier will check this new claim. By factoring  $g_{\text{batch}}^{(i)}$ , it becomes:

$$\begin{split} v_{\text{sum}} &\stackrel{?}{=} \left( \tilde{\text{add}}_i(\vec{r}_a, \vec{\rho}, \vec{\phi}) + \alpha \tilde{\text{add}}_i(\vec{r}_b, \vec{\rho}, \vec{\phi}) \right) \cdot \left( \tilde{L}_{i+1}(\vec{\rho}) + \tilde{L}_{i+1}(\vec{\phi}) \right) \\ &+ \left( \tilde{\text{mul}}_i(\vec{r}_a, \vec{\rho}, \vec{\phi}) + \alpha \tilde{\text{mul}}_i(\vec{r}_b, \vec{\rho}, \vec{\phi}) \right) \cdot \left( \tilde{L}_{i+1}(\vec{\rho}) \cdot \tilde{L}_{i+1}(\vec{\phi}) \right) \end{split}$$

To verify this, the parties proceed as follows:

• V computes the batched gate evaluations locally (using the assumption in Remark 3.1):

$$v_a \leftarrow \tilde{\mathsf{add}}_i(\vec{r}_a, \vec{\rho}, \vec{\phi}) + \alpha \tilde{\mathsf{add}}_i(\vec{r}_b, \vec{\rho}, \vec{\phi}); \qquad v_m \leftarrow \tilde{\mathsf{mul}}_i(\vec{r}_a, \vec{\rho}, \vec{\phi}) + \alpha \tilde{\mathsf{mul}}_i(\vec{r}_b, \vec{\rho}, \vec{\phi})$$

$\bullet$  P computes and sends the two values V does not know:

$$v_0 \leftarrow \tilde{L}_{i+1}(\vec{\rho}); \qquad v_1 \leftarrow \tilde{L}_{i+1}(\vec{\phi})$$

3. Verifier's Local Check: V checks that the values provided by P are consistent with the sumcheck result.

$$V \text{ checks: } v_{\mathsf{sum}} \stackrel{?}{=} v_a (v_0 + v_1) + v_m (v_0 \cdot v_1)$$

If this check fails, V rejects. Otherwise, V is now convinced of the  $i \to i+1$  reduction if and only if P's two claims from the previous step are true.

- 4. **Batching:** To reduce to one claim, V samples and sends batching challenge  $\alpha' \in \mathbb{E}$  to P.

- 5. Resulting Claim: The two claims are combined into a single, new claim about layer i + 1:

$$\tilde{L}_{i+1}(\vec{\rho}) + \alpha' \tilde{L}_{i+1}(\vec{\phi}) \stackrel{?}{=} v_0 + \alpha' v_1$$

This new claim becomes the input for the next layer reduction (for layer  $i+1 \rightarrow i+2$ ).

Figure 4: GKR Layer Reduction  $(i \rightarrow i + 1)$

Substituting this back into the expression for r:

$$r \le 2\left(d \cdot \log\left(\frac{n}{d}\right)\right) + d = d\left(2\log\left(\frac{n}{d}\right) + 1\right).$$