# HADES: Automated Hardware Design Exploration for Cryptographic Primitives

Fabian Buschkowski<sup>1</sup>, Georg Land<sup>2</sup>, Niklas Höher<sup>1</sup>, Jan Richter-Brockmann<sup>1</sup>, Pascal Sasdrich<sup>1</sup> and Tim Güneysu<sup>1,3</sup>

**Abstract.** While formal constructions for cryptographic schemes have steadily evolved and emerged over the past decades, the design and implementation of efficient and secure hardware instances are still mostly manual, tedious, and intuition-driven processes. With the increasing complexity of modern cryptography, e.g., Post-Quantum Cryptography (PQC) schemes, and consideration of physical implementation attacks, e.g., Side-Channel Analysis (SCA), the design space often grows exorbitantly without developers being able to weigh all design options.

This emphasizes the evident necessity for tool-assisted Design Space Exploration (DSE) for efficient and secure cryptographic hardware. To address this demand, we present the HADES framework. This tool systematically traverses the design space driven by security requirements, rapidly predicts user-defined performance metrics, e.g., area footprint or cycle-accurate latency, and instantiates the most suitable candidate in a synthesizable Hardware Description Language (HDL).

We demonstrate the capabilities of our framework by applying our proof-of-concept implementation to a wide-ranging selection of symmetric and PQC schemes, including the ChaCha20 stream cipher and the PQC standard Kyber. Notably, for these schemes, we present the first hardware implementations featuring arbitrary-order masking.

**Keywords:** Design Automation · Design Space Exploration · Hardware Implementations · High-order Masking · PQC · Kyber · Dilithium · AES · SPN · ARX

#### 1 Introduction

Cryptography is one of the main pillars of the security architecture in modern digital applications that are predominantly relying on physically accessible constrained and embedded devices. Nowadays, cryptographic primitives are ubiquitously used in hardware and software systems and continuously evolve and emerge through community efforts and standardization competitions, e.g., the CAESAR competition for Authenticated Encryption (AE) [Ber19] (2013 – 2019), or the National Institute of Standards and Technology (NIST) standardization for Post-Quantum Cryptography (PQC) [NIS17] (since 2017). Consequently, generation of secure and efficient implementations of classical and emerging cryptographic primitives for a wide range of different devices is essential when implementing advanced cryptographic protocols in complex security architectures.

Hardware implementations are especially preferred in most high-assurance and high-performance application scenarios, due to the large amount of design opportunities and

<sup>&</sup>lt;sup>1</sup> Ruhr University Bochum, Bochum, Germany, firstname.lastname@rub.de <sup>2</sup> Intel Labs, Portland, OR, USA, georg.land@intel.com,mail@georg.land <sup>3</sup> DFKI GmbH, Bremen, Germany

<sup>\*</sup>The author contributed to this work solely during his time at Ruhr University Bochum.

available low-level protections. Particularly modern (asymmetric) cryptographic primitives with their modular structure, often consisting of numerous adaptable sub-components, offer a high number of possible combinations and configurations during implementation. The sharing of primitives or their sub-components between various systems and applications further expands the dimensions of the design space.

As a consequence, developers are often unable to accurately assess how design parameters and choices affect the overall efficiency and security of their schemes. Hence, as design and system complexities increase, *manual* Design Space Exploration (DSE) rapidly becomes unmanageable since optimization for specific constraints turns into a laborious and incremental trial-and-error process, e.g., as recently demonstrated for the hardware implementations of BIKE [RMG22, RBCGG22] and Dilithium [LSG21, BNG21, ?].

With this challenge in mind, the ATHENA project [Gaj] provides a first unified and comprehensive Application Programming Interface (API), aiming to enable a fair comparison and automated performance number generation for hardware implementations. Unfortunately, as demonstrated during its deployment in standardization competitions, complex design configurations still need to be generated in a highly manual process by the development teams since no automated exploration process is available. This still poses a challenge for teams with excellent cryptographic expertise but no background to bring this into hardware.

**Research Challenge.** Evidently, there is a need for automated tools that assist designers and engineers in implementing and exploring primitives efficiently in hardware. Automating the DSE with a primary view on security goals, i.e., automatically weighing design decisions and predicting efficiency outcomes, can accelerate and optimize the development process and enable a faster deployment of new cryptographic systems and protocols.

Clearly, efficiency is not the only challenge for cryptographic implementations in hardware and embedded systems. *Physical implementation attacks* are common threats targeting the implementations of cryptographic primitives in hardware and software. More precisely, Side-Channel Analysis (SCA) [KJJ99] enables adversaries to retrieve secret and sensitive information through observation of the behavior and physical characteristics of a device during the execution of cryptographic operations.

Although a number of sound and effective protection mechanisms, such as masking [CJRR99], have been thoroughly studied and are frequently implemented, the practical realization of these mechanisms remains a manual, fragile, and error-prone task, regardless of an expert's extensive experience in this field. Only recently, Knichel et al. [KMMS22] and Buschkowski et al. [BSG23] presented computer-assisted tools that simplify and automate the protection process – however, without support for automated exploration of cryptographic instances and corresponding design parameters.

Consequently, a security-driven and automated design space exploration in order to find *efficient and secure* hardware instances for cryptographic primitives remains an open research challenge.

Our Contribution. In this work, we present a novel approach to model, design, and describe generic and security-aware cryptographic hardware based on the established principles of hardware design, enabling the automated generation and design space exploration of efficient and secure hardware accelerators. Moreover, we transform our concept into a versatile tool which, due to its abstraction and exploration methodology, allows us to generate efficient and side-channel protected hardware instances for any type of contemporary cryptographic primitives. For this, our tool is particularly designed to rapidly predict user-defined performance metrics during DSE, e.g., area, latency, or randomness quantity, before instantiating the optimal candidate in a Hardware Description Language (HDL).

For the proof-of-concept implementation of HADES, which is publicly available on

GitHub, we follow a modular and highly scalable approach. This includes an extensive library of basic building blocks (so-called *templates*) that we instantiate to build and compose commonly deployed cryptographic primitives under a set of given security requirements, like side-channel protection. To demonstrate its capabilities, we perform a wide range of case studies, generating HDL files for efficient and protected symmetric and PQC primitives. As a further contribution, we are the first to provide arbitrary-order masked Application-Specific Integrated Circuit (ASIC) implementations of Add-Rotate-XOR (ARX) ciphers such as ChaCha20 as well as the PQC standard Kyber that were automatically generated using the DSE of HADES.

Related Work. Wolfs et al. [WAM12] present an Electronic Design Automation (EDA) tool that takes a Haskell-based functional HDL as input and performs automated DSE in order to find the best instantiation. The main differences to HADES are that their work neither features side-channel countermeasure considerations whatsoever, nor the ability of performance prediction. More recently, Knichel et al. have presented AGEMA [KMMS22], a netlist transformer that achieves automated side-channel security, but contrarily to HADES is not capable of DSE. Finally, several previous works focus on machine-learning-based DSE [SW12, DZZ<sup>+</sup>18, LLS19, SW20]. Among other drawbacks of these works, they do not focus on cryptographic applications, thus lack security awareness in comparison to HADES. All these related works are compared to HADES extensively in Section 8.2.

# 2 Preliminaries

In this section, we briefly introduce the Hardware Construction Language (HCL) Spinal-HDL, which serves as the essential basis of the proof-of-concept implementation of HADES. Afterward, we provide a summary of the formal background of our security design, including relevant side-channel countermeasures and protection principles.

#### 2.1 SpinalHDL

SpinalHDL [Spi23] is an HCL embedded into the Object-Oriented Programming (OOP) language Scala. In general, HCLs can be used to describe the functionality of a hardware circuit at a higher level of abstraction than traditional HDLs such as VHDL or Verilog are capable of. For this, HCLs are equipped with powerful libraries and convenience features to ease the process of describing hardware while still having complete control over low-level implementation details such as the insertion of registers.

SpinalHDL offers, among other features, dedicated functionalities to describe Finite State Machines (FSMs) and counters. Together with Scala, SpinalHDL offers a wide range of options for the parametrization of hardware designs. In order to integrate into the classical hardware design flow, SpinalHDL additionally provides the necessary translation layer to both standard VHDL and Verilog. Established synthesis tools can then be used to process the resulting hardware descriptions further. Through its black-boxing feature, SpinalHDL is additionally capable of including existing HDL Intellectual Property (IP) into a design with minimal effort by only defining the corresponding interface.

#### 2.2 Masking

After Kocher et al. presented the first side-channel attack on cryptographic implementations in 1999 [KJJ99], many concepts to protect against this attack vector have been presented over the last two decades. Masking, which is based on Shamir's secret sharing [Sha79], has been established as the most promising countermeasure. To share a secret x, it is split into d+1 shares such that  $x=x_0\circ x_1\circ ...\circ x_d$ . For our work, we consider Boolean masking

where the operator  $\circ$  is replaced with an XOR operation. A correct and secure sharing is achieved by choosing d shares uniformly at random (say the first d shares) and computing the remaining share  $x_d$  by  $x_d = x \oplus \bigoplus_{i=0}^{d-1} x_i$ . Applying this approach ensures that an adversary is not able to learn anything about the secret values by having access to up to d shares.

In order to implement a masked design, it is not sufficient to share all inputs, outputs, and intermediate data. All functions that operate on these values also need to be adapted to work with the new shared representation. For linear functions, this is straightforward by applying them individually to each share. However, adapting non-linear functions is much more challenging and error-prone, even with long-standing experience.

To ease this process, research focused on the development of atomic units, so-called gadgets, which are used to replace insecure Boolean gates to achieve protection against SCA. While the developed gadgets are secure against SCA, combining them into a larger circuit does not necessarily yield a secure circuit. As a consequence, the security of gadgets is evaluated under certain composability notions that ensure the resistance of the composed circuit against SCA. Here, the most notable and state-of-the-art composability notion is Probe-Isolating Non-Interference (PINI) [CGLS21], which allows trivial composition of gadgets if those gadgets are PINI as well. Together with the PINI notion, Cassiers et al. introduced the concept of Hardware Private Circuit (HPC) and the corresponding HPC1 and HPC2 gadgets. Recently, Knichel and Moradi proposed HPC3, reducing the latency of the multiplication gadget to one clock cycle [KM22b].

# 3 Design Rationale

Implementing hardware modules for cryptographic primitives in constrained applications often requires a rigorous design space exploration to identify optimal or suitable hardware parameters and component configurations that fulfill specified design requirements. With increasing design complexities and sophisticated system architectures, however, it becomes more and more difficult to precisely determine the interaction of various parameters and configurations, which gets even more challenging if additional protection against physical implementation attacks is required.

## 3.1 Problem Definition

To underline the need for automated support in cryptographic hardware design, we recapitulate the common design steps in the development of hardware modules:

- 1. Specification: The design goals are defined, considering external constraints such as area demand (cost optimization) and latency (constrained by the module application). For cryptographic hardware, additionally, a careful analysis of the adversary model must be carried out, including potential (physical) attack surfaces, such as side-channel security. This results in additional design goals on the targeted level of hardware security.

- 2. **Functional Design**: The developer generates HDL code to implement the desired functionality, potentially following different design approaches (e.g., top-down vs. bottom-up). This manual process usually involves many separate and ad-hoc design decisions many for symmetric cryptography but even more for asymmetric cryptosystems. Each of those decisions impacts the overall performance metrics as well as potential design choices occurring later in the process.

- 3. **Synthesis**: The hardware description is synthesized into a netlist. Subsequently, the functional correctness and post-synthesis area and delay can be assessed. However,

a meaningful verification of implementation security is not possible until Step 6. Moreover, even though a first shortcut back to Step 2 can be taken in case functional correctness or the post-synthesis assessment do not yield the desired results, this reiteration already requires a manual adjustment of the implementation.

- 4. **Technology Mapping**: The synthesized design is mapped onto the target technology, ensuring compatibility and efficiency.

- 5. **Place and Route**: The physical layout of the design on the target device is optimized under consideration of timing, power, and area factors.

- 6. Verification and Validation: In the iterative verification and validation phase, the functional correctness of the final design is tested against diverse input conditions, and the performance of the design is compared to the defined design goals. Simultaneously, the hardware security can be tested by physical measurements as well as verification tools. Feedback from each validation iteration is used to adjust the HDL code until the design goals are met. Thus, a reiteration from the second step is required, most importantly resulting in another manual adjustment of the implementation.

- 7. **Deployment**: The final design is sent to a foundry where the chip is fabricated.

With this current workflow that relies on HDL-based toolchains, two main challenges remain: First, whether or not design goals are achieved is determined at the very end of the design process, after the first iteration of validation (Step 6). However, we ideally want to be able to estimate whether a design meets its defined performance and hardware security goals before Step 3, the synthesis, which is the first of four subsequent computationally expensive and time-consuming operations in the flow. The goal is, thus, to reduce the number of iterations over Steps 3–6 in order to reduce computational cost and development delays. Second, due to the lack of security-by-design integration into the toolchains, fulfilling hardware security goals is an error-prone process that leads to more validation iterations and, thus, more development costs.

Both challenges have their foundation in the fact that the decision-making for design options entirely relies on the developer's experience and intuition, where, ideally the workflow should instead provide tools to enable informed decisions. While this is true for hardware development in general, the hardware security requirements of cryptographic modules add another dimension to the design space, magnifying the complexity of decision consequences. Hence, the synthesis step – before which these decisions are made – is the crucial point that we want to pre-empt with our tool in order to reduce the necessary number of iterations over Steps 3–6.

We identified the following features to solve the aforementioned challenges in the development process that are currently not supported with conventional HDLs:

- Integration of security-oriented design considerations (e.g., to defeat physical attacks by including side-channel countermeasures) into the workflow (cf. Section 3.2.2).

- Automated pre-evaluation of different design options *before* synthesis while guaranteeing their functional correctness (cf. Section 4.1).

- Prediction of certain performance metrics *before* synthesis to enable a swift design space traversal given many thousands or millions of design configurations (cf. Section 4.3).

## 3.2 Templates

To address the above-stated features, we introduce our concept of nested hardware templates with intrinsic support for security requirements as a fundamental principle for the

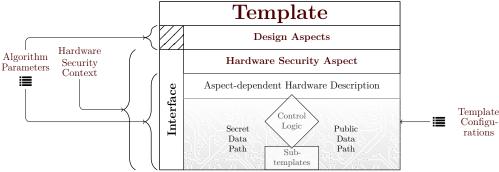

**Figure 1.** The concept of security-aware hardware templates. Here, a template defines a module implementing specific functionality like an adder. As depicted, the Design Aspects (e.g., the adder type in the case of an adder template) do not influence the interface. In contrast, the Hardware Security Aspect (e.g., gadget type) may change the interface (in this example, the number of shares). The actual hardware description then dynamically depends on the aspects.

abstract modeling and performance prediction of arbitrarily complex hardware circuits for cryptographic primitives. This concept, shown in Figure 1, is explained in this section, while details on template processes and their interactions with template internals are explained in Section 4. In Figure 2, we show an excerpt from the Keccak template as a running example to highlight the different template settings and workflows. To highlight how templates intrinsically support hardware security requirements, we additionally show a small excerpt from the Template class, the base for all templates, in Figure 3. It should be noted that template designers do not need to modify this class unless they want to add a new hardware security context or hardware security aspect.

Our hardware templates are characterized by their extensibility and customizability in terms of application-specific algorithm parameters, template configurations, and the hardware security context, as depicted in Figure 1, enabling us to predict a design's performance characteristics without full instantiation of the system. Using a black-box representation, each template defines the interface (data transmission) and functionality (data processing) of an abstract hardware component. This versatility introduces the ability to address diverse use cases with their unique requirements.

To capture the many different ways how a hardware component can internally achieve the desired functionality and security, our templates can be further customized by design and hardware security aspects (Section 3.2.2). The concrete implementation of a template's functionality is then covered by a hardware description that depends on both of these aspects (Section 3.2.2), potentially utilizing various subtemplates. In contrast to modern HDL component representations, e.g., in terms of entities (VHDL) or modules (Verilog), our concept has the hardware security context closely associated, which particularly enables the generation of secure designs by replacing sensitive functionality with secure counterparts. Through additional template metadata (Section 4.2), our concept intrinsically enables a performance prediction, which conventional HDLs can only achieve through the integration of new features. This integral capability streamlines the design process by eventually enabling efficient DSE.

In addition to the advances in abstract modeling and performance prediction, our approach promotes a clear separation between template *designers* and template *users* (Section 4), thereby improving reusability and modularity. Unlike the common practice workflow, where this separation is often implicit and not actively encouraged, our framework promotes a more deliberate division of responsibilities. The template designer, who has specialized knowledge of the intricacies of the hardware and any sensitive parts, focuses on creating extensible, customizable, and secure hardware templates with a strong understanding of the various implementation options and their influence on performance

```

case class Keccak(w : Int = 64) extends Template {

10

val io = new Bundle { //Interface

val stateIn = in Vec(Vec(spinal.core.Bits(w bits), 5), 5) //Input

11

val stateOut = out Vec(Vec(spinal.core.Bits(w bits), 5), 5) //Output

12

13

14

var chiParallel : Int = 64 //Parallelism for Chi step

override def getOptions(): Map[String, Configurable] = Map( //Design aspects

16

"parallelism" -> IntegerList(List(1, 2, 4, 8, 16, 32, 64))

17

override def configure(options: Map[String, Any]): Unit = { //Configure with Template Configuration

18

chiParallel = options("parallelism").asInstanceOf[Int]

19

20

override def instantiate(): Boolean = { //Hardware description

21

val chiIn, chiOut = Vec(Vec(Bits(w bits), 5), 5) //Chi input and output

22

43

for (z <- 0 until w) {</pre>

44

for (x <- 0 until 5) {</pre>

for (y <- 0 until 5) {

45

val zOff = (z+chiParallel) % w

46

if (z < chiParallel) {</pre>

47

chiOut(x)(y)(z) := Xor(chiIn(x)(y)(zOff), And(Not(chiIn((x+1)%5)(y)(zOff)),

chiIn((x+2)\%5)(y)(z0ff)))

49

} else {

50

chiOut(x)(y)(z) := chiIn(x)(y)(zOff)

51

52

54

val chiLatency = latencyAnd + latencyXor + latencyNot + 1 //Latency of the Chi function

71

this.latency = 24 * (1600 / (chiParallel*25) * chiLatency + 3) //Total latency of Keccak

this.reload = this.latency

72

73

true

}

74

```

Figure 2. Excerpt from the Keccak template, showing the template settings as well as the hardware description for the  $\chi$  step. Note that some lines are omitted, for example those containing import clauses.

and security. On the other hand, the template user, liberated from concerns about the functional correctness of the template or its security features, can seamlessly generate a variety of functional and secure designs while using the designed templates.

The modular approach presented above fosters an agile development process while ensuring functional correctness and supporting the integration of security features, essentially moving the hardware development towards security-aware cryptographic libraries instead of static modules. This shift is in line with the dynamic, tool-assisted nature of modern development practices and allows for greater adaptability to new cryptographic requirements while facilitating a more responsive and efficient development cycle.

#### 3.2.1 Template Settings

During the design process of templates, each template in the hierarchy of the hardware model definition is parametrized and configured with three different kinds of settings, as depicted on the left and right side of Figure 1:

Algorithm Parameters are immutable under DSE since they define the inherent algorithmic functionality and external interface of each template in the cryptographic primitive. For hierarchical hardware models and nested templates, this specifically requires the inheritance of algorithm parameters to extend the parametrization to all child templates consistently. As depicted in the very left part of Figure 1, the algorithm parameters can influence the interface and logic (lower part), as well as the available design aspects (upper part). Example: The width of the Keccak function,

```

abstract class Template() extends Component with BooleanGadget with GlobalConfigUser {

val gadgetConfig = GlobalConfig.config.gadgetConfig

gadgetConfig.numShares = gadgetConfig.securityOrder + 1 //Hardware security context

gadgetConfig.latencyAnd = 1 //Hardware security aspect: HPC3 gadget

gadgetConfig.randomnessAnd = gadgetConfig.securityOrder * (gadgetConfig.securityOrder + 1) //HPC3

var latencyAnd = gadgetConfig.latencyAnd

}

var latencyAnd = gadgetConfig.latencyAnd

}

```

Figure 3. Excerpt from the Template-class, highlighting how the hardware security context and aspects influence template internals.

which is defined in Line 9.

**Template Configurations** are application-independent and mutable under DSE. They solely define how template-internal data processing mechanisms are implemented in order to realize the intended functionality. Consequently, template configurations do not affect the external functionality or interface of the given template to ensure consistency throughout the DSE process. Example: The number of concurrently executed  $\chi$  functions for Keccak. The different options for the parallelism, defined in Line 16, modify how the  $\chi$  step is implemented in Line 47.

Hardware Security Context: This defines a security-aware design flow by describing the security level of sensitive data processing or control parts within the template. As shown in the left part of Figure 1, it may impact the interface because data might be passed and returned redundantly, as well as the available hardware security aspect. Similar to algorithm parameters, the hardware security context is immutable under DSE. Example: The masking degree to counter side-channel attacks or other parameters related to the implementation security, such as the amount of redundancy to counter fault-injection attacks. In Figure 3, the hardware security context is the masking degree, which impacts the number of shares in Line 12 as well as the amount of randomness needed for logic gates in Line 14.

Note that the settings are either application-specific and immutable under the DSE or application-independent and mutable. This strict differentiation facilitates functional correctness, as the template user only defines the application-specific settings and can still be sure to receive a functional design after DSE.

Moreover, our approach significantly differs from the traditional development process with HDLs. In VHDL/Verilog, the parametrization is often limited to static configurations, and even the few dynamic options (e.g., generics) do not offer the degree of flexibility necessary for the different application-independent requirements during DSE. Our approach, on the other hand, not only allows for a dynamic adjustment of configurations during DSE but also ensures that the template user's input is largely limited to application-specific settings, promoting a clearer and more user-friendly design process. The adaptability and granularity of our parametrization and configuration model contribute to improved functional correctness and ease of use, making it a more responsive and efficient alternative to traditional HDLs.

#### 3.2.2 Template Internals

Recall that we differentiate between the template developer<sup>1</sup> and its user. The former defines the behavior of a template depending on its algorithm parameters, template configurations, and hardware security context. As this process shares some similarities to

$<sup>^{1}</sup>$ We use the term designer synonymously.

writing hardware descriptions with generics in a traditional HDL, experienced hardware developers can seamlessly adapt to our new workflow.

To enable an efficient DSE with functional and security-aware hardware modules as a result, the following internals are defined by the template developer:

Design Aspects: Depending on the intended functionality, the template designer defines a list of design aspects that represent the freedoms in data processing. Each design aspect then has several aspect options, of which one can be chosen. For example, the parallelism degree of a template could be a design aspect, with a set of integers as its associated options. In our running example, one design aspect (parallelism) is defined in Line 16, with the aspect options being the first powers of two. Design aspects do not interfere with the interface nor the high-level functionality of the template but solely change how the intended functionality is internally achieved. On the other hand, however, the design aspects and their options may be impacted by the algorithm parameters, e.g., the available range of unrolling might depend on the Advanced Encryption Standard (AES) security level. In Figure 1, this duality can be observed by the fact that the algorithm parameters are shown as input to the design aspects, but the design aspects are placed disjoint to the interface.

Hardware Security Aspect: Similar to the design aspects, different aspect options to instantiate the security-sensitive parts may be defined depending on the given hardware security context. For example, if the security context defines a masking degree, multiple types of gadgets to protect the secret data path may achieve the same security level but can have different performance characteristics. Then, each gadget type is a potential option for the hardware security aspect. Figure 3 shows how the chosen hardware security aspect, in this case the HPC3 gadget, changes the latency of logic gates (Line 13) and the needed randomness (Line 14) (we omit similar lines for the other types of logic gates). The HPC2 and HPC3 gadgets are predefined hardware security aspects in the Template class, but further gadget types can be added by template designers. In Figure 2, the chosen hardware security aspect influences the calculation of the  $\chi$  step in Line 48 as well as the definition of the latency in Line 70 due to the different latencies of masked gadgets.

Hardware Description: The tuple of selections for (a) the design aspects and (b) the hardware security aspect is what we call a template configuration. Given a template configuration, a template can be instantiated, which means that a specific design is generated. For this, the template designer gives a hardware description relative to each design aspect such that any combination of options can be instantiated. An excerpt of the hardware description of the Keccak template, namely the  $\chi$  step, is shown in our example starting from Line 21. The selected parallelism is utilized in Line 47, limiting the total number of  $\chi$  operations that are performed in parallel. If a combination cannot be instantiated, e.g., due to mutually exclusive options or because an option is not yet implemented, the designer flags it as a conflict by returning false in Line 73. A conflict will be handled by the configuration extraction procedure accordingly.

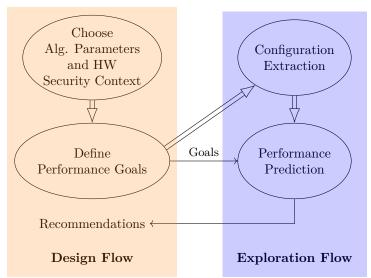

#### 4 Workflow

As depicted in Figure 4, we separate between the design and exploration flow of templates. In this section, we present further details about the individual flows that arise from this separation and consequently enable the efficient DSE and generation of secure designs.

We want to stress that our concept is not designed as a replacement to standard workflows in hardware development but as an essential extension to accommodate the security

Figure 4. Overview of the design and exploration flows.

context. With the final output being standard VHDL or Verilog, our proposed workflow can be integrated into the established hardware toolchain. In particular, our concept extends Step 2 from the common digital design flow ("Functional Design", cf. Section 3.1) to reduce the necessary iterations that stem from Step 6, the verification and validation.

The design flow (left part of Figure 4) starts with the template user choosing the algorithm parameters that match the current use case. Furthermore, the user specifies the hardware security context according to their threat analysis and attacker model. Finally, the user defines the performance goals and which Performance Metrics (PMs) to optimize and eventually receives the recommendations for the best-performing designs, which can then be further processed by synthesis tools. In the following, we focus on the exploration flow (right part of Figure 4), which is much more complex and covers those areas that we aim to automate with our work.

In general, DSE can be employed to achieve the following two goals: (i) finding designs that meet specific performance requirements or (ii) selecting designs with optimal predicted performance among all possible candidates. The DSE for the first approach may terminate as soon as the predicted performance meets all requirements, while the trivial solution for the second approach is exhaustive design space traversal. Yet, more sophisticated methods and, in particular, heuristics may speed up the search for a global optimum or an approximation thereof, which we further discuss in Section 4.4.

Consequently, our concept of nested hardware templates is particularly designed to enable both DSE objectives efficiently. The prerequisite for a traversal of the entire design space is the extraction of all possible design configurations from the template hierarchy. We refer to design configurations as the configuration of the entire template hierarchy, as opposed to template configurations, which are configurations specific to one template.

#### 4.1 Configuration Extraction

The configuration extraction (cf. Figure 4) is presented in Algorithm 1. Using this algorithm, a comprehensive list of available template configurations and potential dependencies is extracted for each (sub-)template in the template hierarchy, excluding those configurations that were flagged as a conflict by the template designer. This check for conflicts is performed in Line 15. In our running example, the extraction of the available template configurations for the Keccak template is done via a simple function call in Line 15.

**Algorithm 1** Configuration extraction procedure. Here,  $P_{a,h}$  is a template parametrized with algorithm parameters a and hardware security context h.

```

1: procedure EXTRACTCONFIGS(P_{a,h})

C := \emptyset (the set of configuration tuples)

D := \text{design aspects of } P_{a,h}

3:

for all d \in D do

4:

O_d := possible options of d

5:

H := \text{hardware security aspects of } P_{a,h}

6:

7:

C_P := H \times O_{d_1} \times \ldots \times O_{d_{|D|}}

▶ Each element is one configuration

for all c \in C_P do

8:

9:

S_c := subtemplates of P_{a,h} when configured with c

10:

for all s \in S_c do

a' := \text{DeriveAlgParameters}_c(a, h)

▷ Defined by designer

11:

C_s := \text{ExtractConfigs}(s_{a',h})

12:

C_c := C_{s_1} \times \ldots \times C_{s_{|S_c|}} \triangleright Each \ entry \ in \ C_c \ is \ a \ tuple \ of \ subtemplate \ configurations

13:

for all \gamma \in C_c do

14:

if \gamma is not flagged as conflict then

15:

extend \gamma with (P_{a,h},c)

16:

C := C \cup \{\gamma\}

17:

return C

18:

```

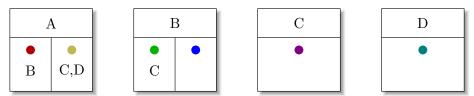

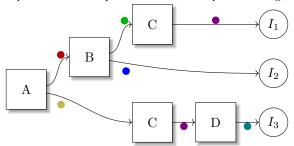

Essentially, Algorithm 1 traverses a decision tree of configuring templates and their subtemplates. This tree walk is depicted exemplarily in Figure 5. Note that the tree in Figure 5b displays the order in which the templates are configured rather than the template hierarchy, as particularly evident by the fact that D is no subtemplate of C. In fact, the layers of the decision tree are exchangeable to a certain extent: In this example, C and D can be exchanged since they are independent of each other.

As explained before, continuously ensuring the functional correctness of each design configuration under evaluation requires a strict top-down configuration procedure, which is ensured by the recursion in Algorithm 1. The input template is parametrized with a set of algorithm parameters and a hardware security context. Eventual subtemplates are parametrized with the same hardware security context as it is immutable during DSE. The algorithm parameters of the subtemplates are, on the other hand, either chosen statically by the template designer or derived from the algorithm parameters and the hardware security context of the current template, as shown in Line 11.

#### 4.2 Performance Prediction

Prediction of PMs is a fundamental process required to guide the DSE and evaluate the suitability of different design configurations of a cryptographic primitive with respect to the specified design requirements. To achieve this, each template predicts various PMs based on its algorithm parameters, template configuration, and the hardware security context, as depicted in the bottom part of Figure 4.

For appropriate choices of PMs and their corresponding prediction, we identified the following requirements and conditions:

**Accuracy:** The PM prediction needs to be reliable in order to correctly select design configurations that meet the intended performance goals and targeted requirements.

**Efficiency:** Estimation of PMs must be fast in order to explore different design options efficiently during DSE. This not only includes computationally efficient prediction routines of PMs but also the utilization of minimal data on design characteristics

(a) Four exemplary templates, where the colored dots depict the configurations and the letters below them describe the subtemplates that are required in case the template is configured that way.

(b) Decision tree that is traversed by Algorithm 1 when template A from Figure 5a is used as the top-level template.

**Figure 5.** An exemplary depiction of templates, configurations, and how configurations are extracted by Algorithm 1.

(while still ensuring accuracy). To emphasize the need for high efficiency, consider our case study of Kyber-CCA, which has over one million possible configurations (cf. Table 10). If estimating the PMs for each configuration took one second, the whole DSE process would take nearly two weeks to complete, which is not feasible in most cases. We further discuss this in Section 8.1.

Coverage: The more hardware module characteristics, e.g., latency, throughput, area utilization, or power consumption, are taken into account, the better a holistic exploration under consideration of various design trade-offs is possible. As the inclusion of more characteristics generally results in a less efficient performance estimation, a careful selection of the most important and meaningful characteristics for the given use case is necessary. For instance, while the power consumption might be critical for a design targeting a constrained device, it can potentially be ignored in a different use case where it is of lesser importance.

While PMs can generally be chosen and defined by the user, a cycle-accurate latency metric is essential in order to generate functional designs and guarantee their correctness. In particular, due to our nested hardware template model, modifications to the template configuration of subtemplates may also impact the latency of the parent template. Therefore, cycle-accurate latency specification is mandatory and must be implemented in any case. In our running example, the latency of the template is specified in Line 70 and Line 71, where it is calculated based on the selected parallelism, the latency for a single execution of the  $\chi$  function (which depends on the latency of different logic functions, which in turn depends on the hardware security context and the selected option for the hardware security aspect), and some constants.

Similarly, we require a template to report a cycle-accurate reload, i.e., the number of cycles to wait until the next input is accepted. This allows for precise scheduling and ensures that data can be fed into the system at the correct intervals without causing data hazards or stalls. In our running example, the reload is specified in Line 72. It is equal to the latency as the Keccak design is not pipelined and can only accept new inputs once the previous computation is completed. By enforcing a cycle-accurate reload metric, we can avoid issues such as pipeline bubbles or under-utilization of hardware resources. Both the

latency and reload metrics are crucial in optimizing the overall design and ensuring the system meets its performance and functional requirements.

When chosen accordingly, the PMs provide quantitative performance measures while their combination further enables trade-off analysis and balanced design decisions. In contrast to existing manual DSE, which mostly relies on intuition, designer experience, iterative design enhancements, and post-synthesis evaluation, our pre-synthesis and metric-based analysis *objectively* guides design space exploration and candidate selection. Ultimately, pre-synthesis prediction of PMs enables advanced search space traversal strategies alongside micro-optimizations, e.g., in terms of early-stage evaluation and subtemplate prioritization or iterative subtemplate refinements (see Section 4.4). Particular examples for PMs include, apart from the aforementioned cycle count latency, the area, power consumption, or critical path delay.

#### 4.3 Performance Prediction Accumulation

Based on the generated list of conflict-free design configurations, the actual DSE procedure iteratively selects design configurations and configures the hardware model accordingly. For this, a top-down procedure is applied, ensuring that only those subtemplates are configured that are eventually instantiated given their parents' configuration. In our running example, the template is configured with the currently selected parallelism in Line 18, overwriting a local variable that is used in the hardware description of the template.

Upon completion of design configuration, the templates estimate, accumulate, and report the user-specified PMs in a bottom-up process, i.e., starting with the lowest level until the top-level template is reached, yielding the final performance prediction. To accumulate the PMs of a template and its subtemplates, each template either provides a customized aggregation function defined by the template designer or uses simple accumulation of PMs as the default procedure.

The default accumulation procedure for the area and randomness PMs of a template is shown in Algorithm 2. The recursive algorithm is first executed for all subtemplates in Line 5, returning the area and randomness PM for each subtemplate, which are then added to the accumulators of the current template. Afterwards, Algorithm 2 estimates the area and randomness for the hardware description of the current template. For this, the procedure iterates through all logic gates (e.g., AND, XOR, NOT, cf. Line 48 in our running example) and registers that are used in the template and counts their occurrences. Afterwards, the number of occurrences for each gate type is multiplied with its approximate size or randomness demand and added to the accumulators.

If the DSE objective is to find a design that fulfills specific performance requirements (i), either the current configuration meets these requirements, or the DSE procedure continues until a suitable candidate has been found. In case the user wants to find the optimal design across all possible candidates (ii), the design space is explored exhaustively and the best configuration is identified. Due to the inherent link between some PMs (e.g., a lower latency often results in a higher area, and vice versa), optimizing all PMs independently is usually not possible. Instead, the DSE optimizes either a single PM or, alternatively, a meta-PM that combines multiple PMs, e.g., the product of area and latency.

#### 4.4 Efficiency

Searching the design space exhaustively may result in impractical run times since the design space grows exponentially in the depth of templates. In this context, it is important to recall that the configuration extraction is expected to be very efficient, as it is a simple graph walk, while performance prediction on the other hand is computationally more significant. Therefore, several measures can be taken to reduce the run time complexity.

**Algorithm 2** Performance accumulation procedure for the area and randomness of a template P.

```

1: procedure AccumulatePerformance(P)

2:

A := 0

R := 0

▶ Initialize area and randomness count with 0

3:

S := subtemplates of P

4:

for all s \in S do

5:

(A_s, R_s) := ACCUMULATEPERFORMANCE(s)

6:

A := A + A_s

7:

R := R + R_s

▷ Accumulate area and randomness for every subtemplate

8:

9:

for all l \in L do

\triangleright L is a list of all gate types used in P

n_l := \text{CountGates}(P, l)

\triangleright Count the number of occurrences of gate l in P

10:

A := A + n_l \cdot \text{SIZE}(l)

11:

R := R + n_l \cdot \text{RANDOMNESS}(l)

12:

return (A, R)

13:

```

#### 4.4.1 Breakpoints

To break the exponential growth, we can apply a divide-and-conquer approach to the DSE. For this, the user defines the maximum number of configurations  $c_{\text{max}}$  that shall be explored exhaustively. Once the configuration extraction crosses the threshold of  $c_{\text{max}}$  configurations, it is relaunched from a different point in the template hierarchy. Specifically, given a current template hierarchy depth of d, it is relaunched independently for all templates that sit a depth  $\lfloor d/2 \rfloor$ . This splitting is repeated until the total number of configurations does not exceed  $c_{\text{max}}$  anymore.

Subsequently, performance prediction is carried out separately on each resulting split part of the template hierarchy with new depth  $\lfloor d/2 \rfloor$  in bottom-up direction. Only the best-performing candidate for each of these parts, according to the target metric, is then passed to the respective top-level template.

It is important to note that for non-combined PMs, this approach is as accurate as an exhaustive search. For example, choosing options with the lowest area footprint bottom-up will always result in the smallest overall design. Conversely, this approach is more inaccurate and rather a trade-off between accuracy and DSE efficiency for combined metrics like the area-latency product, where the previous argument does not hold.

#### 4.4.2 Local Search

Local search algorithms [TC23] are a family of metaheuristic algorithms that are frequently used in optimization problems as they are typically able to quickly find a local optimum while being simple and easy to implement. To allow finding optimal configurations with regard to combined PMs, we make use of the simplest form of local search, starting from a (very likely) non-optimal configuration and altering single design aspects until we reach at least a local optimum.

In order to achieve this, we first need to distinguish between design aspects with well-ordered options (usually parallelism options) and those without (e.g., different ways to implement adders). We assume that the well-ordered aspects have a monotone impact on individual performance metrics. The non-well-ordered aspects, on the other hand, first need to be ordered to prepare for the local search. This is achieved by first predicting the combined PM for a user-configurable number of randomly sampled configurations, and then storing the achieved minimum PM for each aspect option. These minima are then taken as keys to order the respective aspect options.

After ordering the options of all design aspects, we conduct the local search as follows:

1. We start with the configuration from the previously selected sample set that offers the overall best combined PM value as it is the most promising to be close to a local minimum. This PM has already been predicted in the preparation step.

- 2. Next we iterate over all design aspects from the currently selected design configuration.

- 3. For each design aspect, we predict the performance for the options that are adjacent to the currently selected option. Adjacency is determined via the given order for the well-ordered aspects or via the estimated order for the non-well-ordered aspects.

- 4. If one of the performance predictions has improved the targeted combined PM, we use this design as our new current configuration and continue improving the next design aspect.

- 5. Once all aspects in the hierarchy have been processed, we check whether at least one has changed; if not so, we stop and return the current design configuration as we have found a local optimum; otherwise, we return to Step 2 and start over with the first aspect.

Evidently, this leads to a local optimum and diminishes the number of performance predictions that have to be carried out. Whether the *local* optimum is also the *global* optimum consequently highly depends on the number of initial samples. Increasing this number leads to a more precise ordering of the non-well-ordered aspects as well as a better starting point for the local search itself. Clearly, however, the number of performance predictions grows when opting to increase the number of initial samples. Eventually, our practical evaluation (cf. Section 8.1) shows that this general instance of local search finds the global optimum in many cases, even with small sample sizes, significantly improving the DSE performance.

# 5 Proof-of-Concept

While Section 3 discusses our general concept for secure and efficient design space exploration and Section 4 presents our proposed workflow, this section briefly introduces and discusses essential aspects of our proof-of-concept implementation of HADES.

#### 5.1 Language Embedding

To implement our proof-of-concept, we require a language or a set of languages that allow us to (i) implement templates with their settings and internals, (ii) express the hardware functionalities of a template, and (iii) perform the DSE.

We opted to follow the OOP paradigm as it trivially allows for the implementation of templates (i) as well as the DSE (iii). In particular, when realizing templates as classes, the template hierarchy can be represented via the instantiation of sub-classes, even when multiple subtemplates of the same type are required. Using the inheritance functionality of OOP, algorithm parameters can simply be propagated from the top-level template to its subtemplates. Furthermore, template internals, such as the design aspects with their possible configuration options or the PMs, can be stored as fields inside the template class. This enables a straightforward configuration extraction and template configuration during the DSE through dedicated class methods and further allows us to access and modify the PM during the performance prediction.

Consequently, we decided to use a HCL embedded into an OOP language to describe a template's functionality (ii). Unlike conventional HDLs that lack essential features for our concept of templates (cf. Section 3.1), HCLs enable a convenient hardware description through their rich features and the integration of the hardware description into the

respective template class. The OOP language Scala with its embedded HCL, SpinalHDL, is a suitable choice as it is among the most feature-rich and well-maintained HCLs that can be augmented with additional properties. Furthermore, the translations to standard VHDL and Verilog ensure that the generated designs can be further processed by the established toolchain for synthesis and placement. Chisel [Chi23], an alternative HCL embedded into Scala, was also investigated regarding its suitability. However, unlike Chisel, SpinalHDL (i) is strongly typed, removing possible sources of errors in the template descriptions, and (ii) its black-boxing feature supports generics, which is especially useful when including existing IP with generics into a design.

We also considered the usage of High-Level Synthesis (HLS) to translate a description from a high-level language, such as C, into a hardware description. This approach would allow for a quick implementation of designs through the rich features of high-level languages and require little knowledge about the underlying hardware from template designers. However, as high-level languages rely mostly on the HLS tools to optimize the performance of a design, it is often impossible to achieve optimal performance, especially for complex cryptographic designs. Certain design aspects, such as an unrolling or pipelining factor, are furthermore often not chosen by the designer but instead determined by the HLS tools, limiting the number of different designs that can be explored during DSE. Finally, as high-level languages lack the ability to express some low-level hardware features such as registers, performance prediction prior to HLS would either be very inaccurate or would require reverse-engineering the HLS algorithms to know how registers are inserted. Given the complexity of current HLS tools, this seems out of reach. Therefore, we deemed HLS to be an unsuitable approach for the hardware description of templates.

## 5.2 Templates

When implementing templates as Scala classes, we have to ensure that the parametrization settings and template internals are implemented in an appropriate way that matches the requirements from Section 3.2 and Section 4.

To represent their immutability during DSE, algorithm parameters are implemented as constructor parameters of the template class. This also allows potential sub-classes to inherit algorithm parameters from the parent class. The hardware security context, which is not only immutable but also identical for all templates in our proof of concept, is implemented as an object that is created at the start of the DSE and shared between all templates. The configurable design aspects and the hardware security aspects are realized as static fields in the template class. This allows the design options to depend on algorithm parameters (cf. Section 3.2.2) and enables access to these options during configuration extraction through a dedicated class method. Finally, the PMs for each template are stored in mutable class fields and can be accessed or modified through dedicated class methods.

#### 5.3 Design Space Exploration

The DSE procedure of our proof-of-concept implementation of HADES currently supports four PMs, namely Latency, Reload, Area, and Randomness. While the latency and reload of a template are computed cycle-accurately based on the information specified and stored in the template by the template designer (cf. Line 71), the area of an instantiated template can only be estimated. This estimation is based on the number of registers and logic templates used in a template and a list containing the sizes of registers and logic templates after synthesis (in Gate Equivalent (GE)). Our implementation is equipped with a list of logic gate and register sizes for the NanGate 45 nm library and can be extended for arbitrary cell libraries. The randomness demand of a design can be accurately calculated based on the amount and type of logic gates used in each template as well as the current hardware security option. As an unmasked design uses zero bits of randomness, this

PM is only viable if a masking degree of one or more is selected. To explore trade-offs between different PMs, our proof-of-concept implementation additionally calculates the Area-Latency Product (ALP) and Area-Latency-Randomness Product (ALRP) by multiplying the respective PMs, yielding balanced designs. Our implementation focuses on the trade-offs between area and latency, as these are typically the most crucial PMs in hardware development. However, additional trade-offs, such as the Area-Randomness Product, can easily be added to the DSE process.

To perform the DSE, our implementation first extracts a list of all possible design configurations according to Algorithm 1. For every found design configuration, the PMs are accumulated using a bottom-up procedure. The PMs of the top-level template, equivalent to the performance of the entire design, are stored in a table together with the corresponding design configuration. Sorting this table by a certain PM allows us to find the optimal design configuration in the respective category. In case of a tie between multiple design configurations (which can typically happen for latency or randomness), the table can be further sorted by a secondary PM to find the best-suited design. Users can additionally specify thresholds for one or multiple PMs that configurations must not exceed. Then, the DSE is performed as before, but only it returns configurations within the specified thresholds, or an error if no suiting configuration was found.

# 6 Case Studies

In this section, we showcase the performance and versatility of our tool and perform DSE on various common cryptographic components and schemes. Notably, we provide implementations of primitives with known implementations in the literature, but also novel implementations, e.g., for ChaCha20 and Kyber, which demonstrates the adaptability of our tool.

For DSE, we aim at an optimization towards five different goals: <u>Latency</u>, <u>Area</u>, <u>Randomness</u> (only for masked designs), <u>Area-Latency-Randomness-Product</u> (only for masked designs), and <u>Area-Latency-Product</u>.

For the synthesis, we use Synopsys Design Compiler, version S-2021.06-SP4, with the NanGate 45 nm library. We do not perform an extensive synthesis optimization but rather set the timing goal to 10 µs, which is typically surpassed by the synthesis tool. It should be noted that the reported performance numbers may be further optimized by a more sophisticated synthesis routine. In order to compute the delay values presented in this Section, we multiply the latency of a template in cycles with the critical path delay as given in the synthesis report. Due to the long synthesis times for some of our designs, we abort the synthesis after 72 hours and highlight the affected designs in the following tables.

Throughout this Section, we use various abbreviations in the tables: Opt. (optimization target), Design Config. (design configuration), Rand. (randomness, in bits per cycle), Lat. (latency, given in cycles), est. (estimated), and T.put (throughput). We further use abbreviations that are specific to case studies: QR (quarter round), pipel. (pipelined), para. (parallelism), arch. (architecture), add. (adder), and comp. (comparison).

#### 6.1 Efficient Addition

Efficient addition has been thoroughly scrutinized throughout the history of electrical engineering. The simplest method is the Ripple-Carry Adder (RCA), which requires a cascade of n Full Adders (FAs) to add two n-bit numbers. In contrast to this, the category of parallel prefix adders achieves a better critical path delay by performing addition with around  $\log_2(n)$  stages of so-called propagate-generate groups. Moreover, both types can be implemented in a serial or pipelined fashion, achieving either a lower area footprint or a higher throughput.

| $\overline{d}$ | Opt.                 | Design               | Config.             | $\mathbf{Are}$     | a                  | Rand.          | Lat.          | Delay                |  |

|----------------|----------------------|----------------------|---------------------|--------------------|--------------------|----------------|---------------|----------------------|--|

| <i>u</i>       | <b>Opt.</b>          | gadget               | adder               | [est. kGE]         | [kGE]              | [bits]         | [cycles]      | [ns]                 |  |

|                |                      | Algorit              | hm Para             | meter: 1           | l6 bit             |                |               |                      |  |

| 0              | L/A/ALP              | _                    | SKA                 | 0.197              | 0.198              | 3 —            | 0             | 0.5                  |  |

| 1              | L/ALP<br>A<br>R/ALRP | HPC3<br>HPC3<br>HPC2 | SKA<br>sRCA<br>sRCA | 8.8<br>1.4<br>1.5  | 6.5<br>1.3<br>1.4  | 116<br>4<br>2  | 5<br>16<br>32 | 1.8<br>42.0<br>55.5  |  |

| 2              | L/ALP<br>A<br>R/ALRP | HPC3<br>HPC3<br>HPC2 | SKA<br>sRCA<br>sRCA | 18.9<br>3.1<br>3.3 | 13.4<br>2.1<br>2.2 | 348<br>12<br>6 | 5<br>16<br>32 | 2.1<br>33.7<br>55.5  |  |

|                |                      | Algorit              | hm Para             | meter: 3           | 32 bit             |                |               |                      |  |

| 0              | L/A/ALP              | _                    | SKA                 | 0.481              | 0.482              | 2 —            | 0             | 0.7                  |  |

| 1              | L/ALP<br>A<br>R/ALRP | HPC3<br>HPC3<br>HPC2 | SKA<br>sRCA<br>sRCA | 20.8<br>2.5<br>2.6 | 16.7<br>2.4<br>2.5 | 304<br>4<br>2  | 6<br>32<br>64 | 2.6<br>73.9<br>107.8 |  |

| 2              | L/ALP<br>A<br>R/ALRP | HPC3<br>HPC3<br>HPC2 | SKA<br>sRCA<br>sRCA | 48.2<br>5.6<br>5.8 | 34.8<br>3.6<br>3.8 | 912<br>12<br>6 | 6<br>32<br>64 | 3.4<br>82.5<br>140.2 |  |

**Table 1.** DSE and synthesis results for an adder up to the second masking degree. Exemplarily, we choose 16- and 32-bit widths, but this value is freely configurable.

In the field of side-channel security, Schneider et al. [SMG15], for the first time, introduced arithmetic addition over Boolean-shared values, which makes use of such traditional adder types. Bache and Güneysu [BG22] extended this to higher-order and gadget-based masking. We refer to their works for a comprehensive comparison of different adder types.

Since adders are the foundation of various cryptographic primitives and higher-level templates, we provide three generic templates with configurable bit width:

- 1. Ripple-Carry Adder (RCA): This template can be instantiated as a serial or pipelined module (further denoted as sRCA and pRCA). The former works with a single FA that incrementally fills a register stage with its result, while the latter deploys n full adders in parallel. Notably, our pRCA template does not feature a dedicated register stage. Hence, without side-channel protection, the pRCA template has a latency of zero cycles. Only when side-channel protection is activated, a cycle count latency is induced by the secure gadgets and, thus, a fully-pipelined design arises, which has the same latency as the sRCA but, naturally, a higher throughput.

- 2. Sklansky Adder (SKA): The SKA has  $\log_2(n)$  propagate-generate stages. Analog to the RCA, there are no dedicated register stages in the template, and only with side-channel protection the latency increases to a minimum of  $\log_2(n)$  clock cycles.

- 3. Kogge-Stone Adder (KSA): The KSA has the same number of propagate-generate stages as the SKA but requires more such groups in parallel, which, positively, yields a lower fanout.

The template library currently features both SKA and KSA as pipelined versions only. An extension of the adder options is subject to future work.

Table 1 shows the results of the DSE on our adder templates and the synthesis results up to the second masking order. It already highlights several trade-offs that can be done on a low level. In particular, the masked serial RCA modules are strictly smaller and require less randomness compared to their parallel-prefix counterparts while having a higher latency and delay. Besides, Table 1 shows that the area estimation is often very close to the final area.

**Table 2.** DSE and synthesis results for modular addition up to the second masking degree. Exemplarily, we choose the moduli of Kyber and Dilithium, but the template allows for the parametrization of any modulus.

| d | Opt.                   | Design               | Config.             | Area                 | a                   | Rand.             | Lat.             | Delay                 |

|---|------------------------|----------------------|---------------------|----------------------|---------------------|-------------------|------------------|-----------------------|

| a | <b>Opt.</b>            | gadget               | adder               | [est. kGE]           | [kGE]               | [bits]            | [cycles]         | [ns]                  |

|   | Algo                   | rithm F              | Paramete            | er: $q = 33$         | 29 (K               | (yber)            |                  |                       |

| 0 | L/A/ALP                | _                    | SKA                 | 0.4                  | 0.4                 | _                 | 0                | 1.0                   |

| 1 | L<br>A/ALRP            | HPC3<br>HPC3         | SKA<br>sRCA         | 15.8<br>2.8          | 16.1<br>2.6         | 208<br>28         | 11<br>61         | 4.7<br>63.4           |

| 1 | R/ALP                  | HPC2                 | sRCA                | $\frac{2.5}{3.5}$    | 3.2                 | 14                | 88               | 81.0                  |

| 2 | L<br>A/ALRP<br>R/ALP   | HPC3<br>HPC3<br>HPC2 | SKA<br>sRCA<br>sRCA | 36.4<br>6.3<br>8.0   | 34.5<br>4.7<br>6.1  | 966<br>84<br>42   | 11<br>61<br>88   | 5.6<br>60.4<br>106.5  |

|   | Algoritl               | nm Para              | ameter:             | q = 83804            | -17 (Ι              | Dilithium         | n)               |                       |

| 0 | $_{\rm A}^{\rm L/ALP}$ | _                    | SKA<br>sRCA         | 0.8<br>0.8           | 0.8<br>1.4          | _                 | 0<br>56          | 1.2<br>54.3           |

| 1 | L/ALP<br>A<br>R/ALRP   | HPC3<br>HPC3<br>HPC2 | SKA<br>sRCA<br>sRCA | 36.1<br>4.9<br>6.2   | 38.2<br>4.7<br>5.8  | 478<br>50<br>25   | 13<br>105<br>154 | 7.5<br>105.0<br>163.3 |

| 2 | L/ALP<br>A<br>R/ALRP   | HPC3<br>HPC3<br>HPC2 | SKA<br>sRCA<br>sRCA | 83.4<br>11.0<br>14.2 | 82.0<br>8.5<br>10.9 | 1434<br>150<br>75 | 13<br>105<br>154 | 6.8<br>115.5<br>201.8 |

#### 6.2 Modular Addition

Several contemporary use cases, such as Kyber, require addition in  $\mathbb{Z}_q$  for non-power-of-two q. For this, we implement an adder template that supports freely configurable moduli q. As proposed in [LMRG24], the general idea is to add the inputs a and b and then subtract q while storing the original addition result. As a result, we have a+b and a+b-q. Finally, we can use the carry-out of the subtraction to select between both results.

The modular addition template utilizes the basic adder templates, automatically choosing the correct bit widths. Consequently, this template can be instantiated as a serial or pipelined module as well, depending on which basic adder type is used. Table 2 shows the DSE and synthesis results for the moduli of Kyber and Dilithium. Interestingly, for the larger q, the serial RCA is chosen for d=0 with area optimization. This is due to the fact that the serial RCA uses control logic and a stage register, which have a relatively high impact on the area for smaller moduli. For larger moduli, the size of the control logic and the state register increases only slightly for the serial RCA, while the additional generate/propagate groups significantly increase the size of the parallel prefix adders.

#### 6.3 ARX Ciphers

Using only the adder templates, we can already securely instantiate a whole family of cryptographic ciphers consisting only of <u>a</u>ddition, <u>r</u>otation, and  $\underline{X}OR$  operations. Notably, the latter two can be performed share-wise for PINI gadgets such as the HPC gadgets. As a representative of this type of cipher, we have exemplarily implemented a template for ChaCha20, configurable for the architecture (round-based or unrolled), adder type (including serial or pipelined), number of quarter rounds to be performed in parallel (1, 2, 4, or 8), and pipelining of the quarter rounds.

Table 3 shows the results of our DSE and the synthesis. The unrolled and fully-pipelined architecture is only selected when optimizing purely for latency or reload since it introduces a significant area overhead that outweighs the savings in terms of latency in

| d        | Opt.   |                        | gn Conf | Are                   | $\mathbf{e}\mathbf{a}$ | Rand.  | Lat.       | Delay  |        |          |           |

|----------|--------|------------------------|---------|-----------------------|------------------------|--------|------------|--------|--------|----------|-----------|

| <i>u</i> | Opt.   | architecture           | # QR    | QR pipel.             | adder                  | gadget | [est. kGE] | [kGE]  | [bit]  | [cycles] | $[\mu s]$ |

|          | L      | unrolled               | 8       | true                  | SKA                    | _      | 192.3      | 176.8  | _      | 10       | 0.06      |

| 0        | A      | $\operatorname{round}$ | 1       | false                 | SKA                    |        | 3.5        | 10.9   | _      | 415      | 0.88      |

|          | ALP    | round                  | 4       | false                 | SKA                    |        | 5.0        | 15.4   | _      | 103      | 0.22      |

|          | L      | unrolled               | 8       | true                  | SKA                    | HPC3   | 7335.6     | 6755.5 | 102144 | 486      | 0.23      |

|          | A      | $\operatorname{round}$ | 1       | false                 | sRCA                   | HPC3   | 14.7       | 22.0   | 4      | 22576    | 52.2      |

| 1        | R/ARLP | $\operatorname{round}$ | 1       | false                 | sRCA                   | HPC2   | 14.8       | 22.0   | 2      | 33328    | 75.0      |

|          | ALP    | round                  | 1       | $\operatorname{true}$ | SKA                    | HPC3   | 95.1       | 99.0   | 1216   | 570      | 1.1       |

|          | L      | unrolled               | 8       | true                  | SKA                    | HPC3   | 16977.9    | n/s*   | 306432 | 486      |           |

|          | A      | $\operatorname{round}$ | 1       | false                 | sRCA                   | HPC3   | 32.5       | 32.3   | 12     | 22576    | 49.9      |

| 2        | R/ALRP | $\operatorname{round}$ | 1       | false                 | sRCA                   | HPC2   | 32.7       | 32.4   | 6      | 33328    | 70.0      |

|          | ALP    | round                  | 1       | $\operatorname{true}$ | SKA                    | HPC3   | 219.4      | 178.8  | 3648   | 570      | 1.2       |

**Table 3.** DSE and synthesis results for ChaCha20 up to the second masking order.

\*not synthesizeable within 72 hours

all implemented combined metrics. Nonetheless, this architecture is able to offer vastly improved throughput compared to all other configurations, with the first-order masked variant running at over 2.1 GHz and thus exceeding a throughput of 1 Tbit/s.

#### 6.4 Keccak

The Keccak family of permutation functions can be used to instantiate hash functions or Extendable Output Functions (XOFs), most notably SHA3 variations and SHAKE. Masking is especially required for use cases in which Keccak processes secret data, such as within Kyber.

The permutation consists of five steps: the first three  $(\theta, \rho, \pi)$  are linear in the Boolean masking domain, the  $\chi$  step is a quadratic function and requires non-linear gates, and the final  $\iota$  step is an affine function. The main parameter to explore during DSE, particularly for masked designs, is the number of parallel  $\chi$  operations to perform. Currently, our template is restricted to Keccak-f[1600] – a generalization is planned as future work – and it supports 25, 50, 100, 200, 400, 800, or 1600 parallel  $\chi$  operations. During each permutation iteration, the first three linear steps are carried out simultaneously within a single clock cycle, and the outcome is then stored in the state register. Afterward, the  $\chi$  step is performed with the configured parallelism, and the  $\iota$  step is performed in a final clock cycle. This procedure is repeated 24 times, as given by the Keccak specification.

For masked designs, most area and all randomness is spent on the quadratic  $\chi$  step, which is the only one to require (costly) non-linear gadgets. Hence, a trade-off exists between low latency (many  $\chi$  operations in parallel) and low area and randomness (few  $\chi$  operations). The trade-off is noticeable in the results of the DSE shown in Table 4.

# 6.5 Advanced Encryption Standard (AES)

AES is one of the most widely used symmetric encryption algorithms, and there are various implementation strategies with different performance characteristics. Therefore, finding the best-suited implementation among all possible designs is of crucial importance, especially when also considering security against physical attacks.

Our AES encryption core is parametrizable for all standardized key sizes, namely 128, 192, and 256-bit keys. During DSE, the following design aspects are explored: The architecture (round-based or unrolled), the types of S-Boxes for the round function and the key schedule (currently Canright or Boyar-Peralta S-Box; different choices are possible), the number of S-Box instances within the key schedule (1, 2, 4, 8), and the number of

| $\overline{d}$ | Opt.         | Desi  | ign Config. | Are        | a     | Rand. | Lat.     | Delay   |

|----------------|--------------|-------|-------------|------------|-------|-------|----------|---------|

| a              | Opt.         | para. | gadget      | [est. kGE] | [kGE] | [bit] | [cycles] | [ns]    |

|                | L            | 64    | _           | 12.9       | 22.0  | _     | 96       | 30.72   |

| 0              | A            | 1     | _           | 6.7        | 16.2  |       | 1608     | 916.76  |

|                | ALP          | 32    | _           | 9.8        | 19.3  | _     | 120      | 115.16  |

|                | L            | 64    | HPC3        | 131.6      | 149.4 | 3200  | 120      | 40.80   |

| 1              | A            | 1     | HPC3        | 15.1       | 30.1  | 50    | 3144     | 1792.47 |

| 1              | R/ARLP       | 1     | HPC2        | 15.9       | 34.6  | 25    | 4680     | 3744.00 |

|                | ALP          | 16    | HPC3        | 42.8       | 61.6  | 800   | 264      | 198.05  |

|                | L            | 64    | HPC3        | 299.3      | 325.9 | 9600  | 120      | 40.80   |

| 0              | A            | 1     | HPC3        | 24.3       | 52.2  | 150   | 3144     | 2954.89 |

| 2              | R/ARLP       | 1     | HPC2        | 26.2       | 54.1  | 75    | 4680     | 2901.43 |

|                | $ m ^{'}ALP$ | 16    | HPC3        | 89.8       | 117.7 | 2400  | 264      | 211.20  |

**Table 4.** DSE and synthesis results for Keccak-f[1600] up to the second masking degree. Latency and delay are given for one permutation consisting of 24 rounds.

parallel S-Boxes (0, 1, 2, 4, 8, or 16) and MixColumns instances (1, 2, or 4) in a round. If the number of round S-Boxes is set to 0, the S-Box instances dedicated to the key schedule are reused. Table 5 shows the results of the DSE. Most notably, at first and second order, the unrolled architecture is chosen when optimizing for latency. Due to the inherent register stages of masked non-linear gadgets, this architecture only halves the latency compared to the round-based ALP optimization while increasing the area by a factor of at least 36.

## 6.6 Polynomial Multiplication

Recently, Land et al. [LMRG24] showcased the feasibility of applying gadget-based masking to modern Public-Key Cryptography (PKC) and particularly lattice-based PQC schemes, by implementing Streamlined NTRU Prime completely with HPC2 gadgets. They observe that polynomial multiplications, as often required by lattice-based schemes, are feasible with Boolean masking if there is a public operand and the secret operand has only a small number of possible coefficient values. In this case, it is possible to deploy schoolbook multiplication. This approach boils down to

- 1. multiplying the coefficient of the public operand by each potential secret coefficient value (this can be done without side-channel protection), then

- 2. securely multiplexing each of these public values with the secret coefficient as the "select" input, and finally

- 3. securely accumulating the mux result using an adder.

The downside of this approach is that implementations of most PQC schemes usually deploy dedicated multiplication routines like Number-Theoretic Transform (NTT) or Karatsuba, which are algorithmically faster but infeasible to use with Boolean masking due to the large intermediate coefficient multiplications.

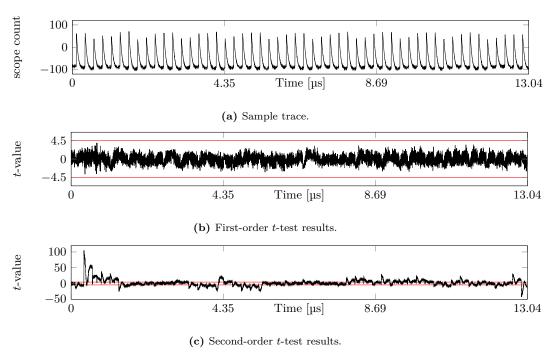

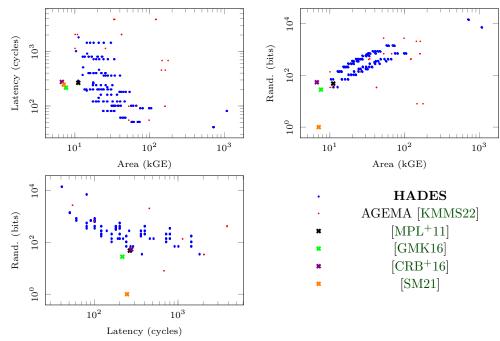

The template we implement follows the schoolbook strategy to enable Boolean masking and features configurability regarding the reduction polynomial, coefficient modulus, adder types, and the number of adders that are instantiated in parallel. Notably, the list of potential numbers of parallel adders is computed individually for each reduction polynomial, such that the search complexity of the DSE remains reasonable. Table 6 contains the DSE results for the polynomial multiplication for the Kyber-512 use case.